最近,有朋友向笔者反馈一个非常蛋疼的问题——iPhone安装了App后,却没法在桌面找到它!这种情况在之前是没有的,为什么现在会出现?这其实和iOS14的一个新特性“App资源库”有关。

2020-10-19 10:04

时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成一个最基本的动作。

2018-03-11 10:07

首先,我们看一下时钟信号中最常见到的波形 - 矩形波(尤其是方波更常用)。在较低时钟频率的系统中我们看到的基本上都是以矩形波为主的时钟信号,因为电路基本上都是靠时钟的边

2018-12-06 11:53

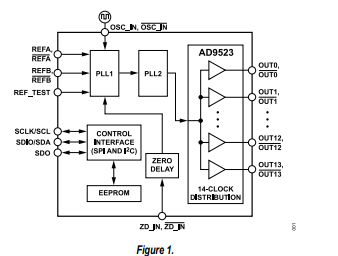

AD9523提供低功耗、多路输出时钟分配功能,具有低抖动性能,还配有片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为3.6 GHz至4.0 GHz。 AD9523

2025-04-10 15:50

SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7个JESD204B转换器或其他逻

2023-06-21 15:10

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20

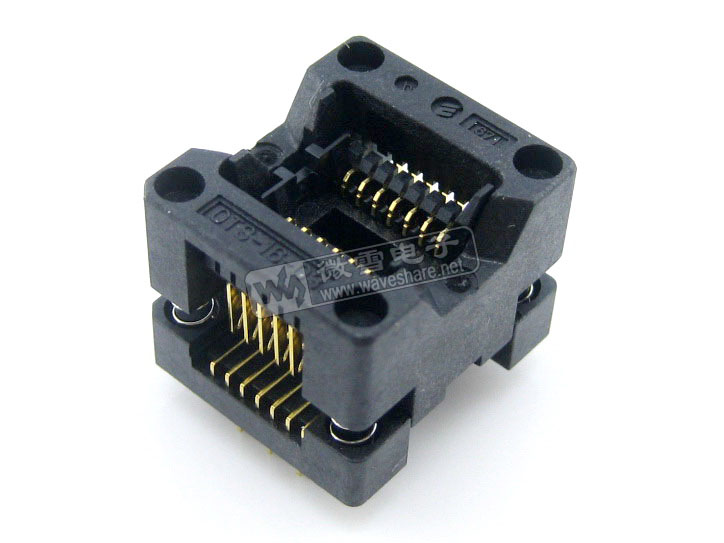

SOP14 SOIC14 SO14 IC引脚间距1.27mm 编程座 测试座 用于SOP14的芯片进行烧写、测试,IC体宽3.9mm 型号 OTS-

2019-12-16 09:10

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题。内部逻辑(组合逻辑)产生的时钟容易出现毛刺,影响设计的功能实现;组合逻辑固有的延时也容易导

2022-10-26 09:04

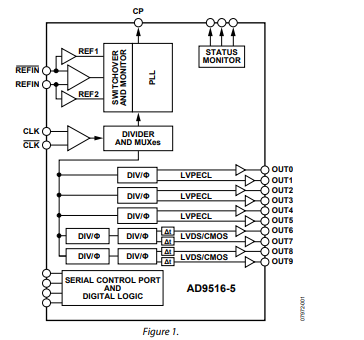

AD9516-5提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO/VCXO使用。

2025-04-11 11:00