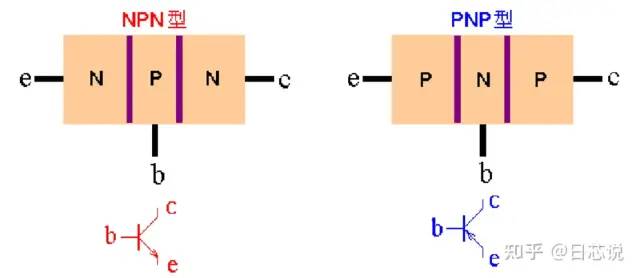

本文谈一谈BJT这个device、以及模拟IC设计师眼中对BJT的了解程度(只用过CMOS工艺的模拟IC设计师)。 BJT即三极管,分为PNP和NPN型,简单示意

2023-02-20 15:47

1. FPGA设计工程师努力的方向? SOPC、高速串行I/O、低功耗、可靠性、可测试性和设计验证流程的优化等方面。 随着芯片工艺的提高,芯片容量、集成度都在增加, FPGA设计也朝着高速、高

2023-03-29 03:25

MEMS模型由系统和IC 设计师使用,因此模型应当尽可能紧密地集成到用户的设计流程。对于IC 设计师,这需要模型支持所有模拟器,具有设计流程中的各种实体化等级的多种视图

2013-01-24 10:27

化的设计。但对那些想通过单一工艺技术提供更高集成度的 RF IC设计师来说,选择最佳工艺技术所面临的最大挑战是灵活性。 在基站的发送器内,模拟I/Q调制器是决定发送信号路径的本底噪声和线性度的关键RF IC器件,不

2019-07-05 07:10

为了了解设计的发展历程,我采访了Silicon Labs的两位资深IC设计师。我们触及了他们最早的IC设计记忆,并讨论了他们对行业未来的愿景,只用回忆和意见,而不是依赖附带的文件。

2020-09-25 10:49

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合技术是数字IC设计师必须掌握的一项核心技术。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:55

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合技术是数字IC设计师必须掌握的一项核心技术。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:52

本课程主要介绍通过逻辑综合工具,将Verilog RTL 代码转换成门级网表的方式,以满足设计的时序要求。学习本课程可以熟悉逻辑综合工具的使用。逻辑综合技术是数字IC设计师必须掌握的一项核心技术。欢迎参与“启芯SoC年度培训计划”,了解详情。

2014-07-03 16:57

Ic载板的设计完全是为符合芯片与封装方式的要求,有关电路布线与互连是由Ic设计师们所完成的,对于制造者更关注的足与Ic载板制造密切相关的设计冈素。在当前数字化时代所追求

2011-12-27 17:08

理解,他们可以打造出优雅的DC-DC转换器设计。然而,IC设计师通常会回避棘手的散热问题——这项工作通常属于封装工程师的职责范围。

2019-10-08 08:30