建立时间和保持时间是SOC设计中的两个重要概念。它们都与时序分析有关,是确保芯片正常工作的关键因素。

2023-08-23 09:44

静态时序分析包括建立时间分析和保持时间分析。建立时间设置不正确可以通过降低芯片工作频率解决,保持

2022-08-22 10:38

本文主要介绍了建立时间和保持时间。

2023-06-21 14:38

信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是接收器本身的特性。简而言之,时钟边

2023-09-04 15:16

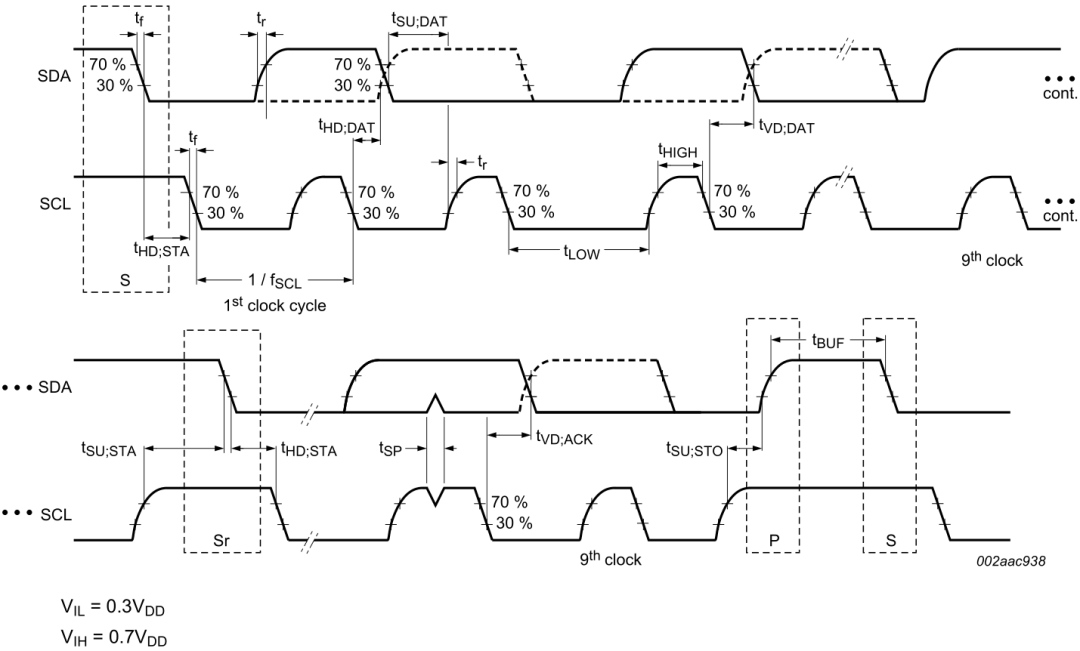

I2C Transfer Definition of timing 想要深入探讨 I2C 协议,必须深刻理解各种时间的定义(F/S-mode) 标识符 定义 tf 信号下降时间

2023-07-25 09:33

在时序电路设计中,建立时间/保持时间可以说是出现频率最高的几个词之一了,人们对其定义已经耳熟能详,对涉及其的计算(比如检查时序是否正确,计算最大频率等)网上也有很多。

2023-06-27 15:43

建立时间(setup time)和保持时间(hold time)是时序分析中最重要的概念之一,深入理解建立时间和保持

2023-06-21 10:44

文件提到两种setup/hold测量方式:10% push-up和pass/fail,按照TSMC说法,前者会更乐观一些,因此如果是采用前者(10% push-up)的测量方式得到建立时间和保持时间,需要十份小心时序

2023-12-05 11:19

建立时间和保持时间贯穿了整个时序分析过程。只要涉及到同步时序电路,那么必然有上升沿、下降沿采样,那么无法避免setup-time 和 hold-time这两个概念。 1. 什么是setup-time

2017-02-08 14:48

今天有个小伙伴遇到一个问题,就是在vivado里面综合后看到的建立时间和保持时间裕量都是inf,我们来看看怎么解决这个问题。

2023-07-30 10:26