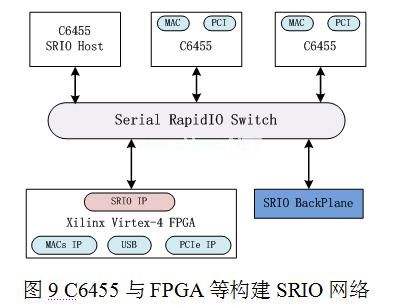

基于TMS320C6455的高速SRIO接口设计 引 言 数字信号处理技术已广泛应用于通信、雷达、声纳、遥感、图形图像处理和语音处理等领

2010-02-24 16:58

FPGA的SRIO(Serial RapidIO)接口使用时,需要注意以下几个方面以确保数据交换和通信的顺利进行: 接口连接与配置 : 确保FPGA和与其通信的设备(如DSP)上都配备了

2024-06-27 08:33

最近做了个4片6678全互联的板子,想在投板前仿真下,现在就缺少6678 SRIO接口的AMI模型,请问TI工程师怎么才能获得这个模型?

2020-07-30 11:24

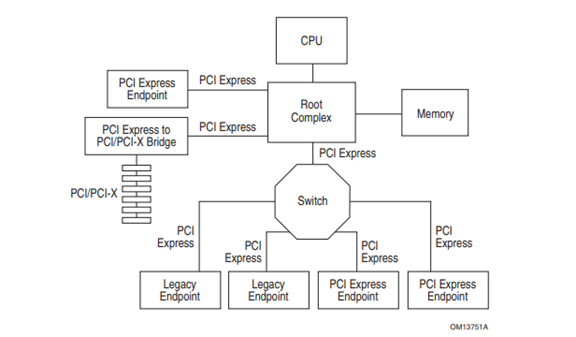

随着PCIe接口、以太网接口的飞速发展,以及SOC芯片的层出不穷,芯片间的数据交互带宽大大提升并且正在向片内交互转变;SRIO接口的应用市场在缩小,但是由于DSP和Po

2022-08-02 10:00

目前具备SRIO接口的硬件不多,推荐广州星嵌电子科技有限公司开发的DSP+FPGA+RAM开发板XQ6657Z35-EVM。

2022-11-08 17:22

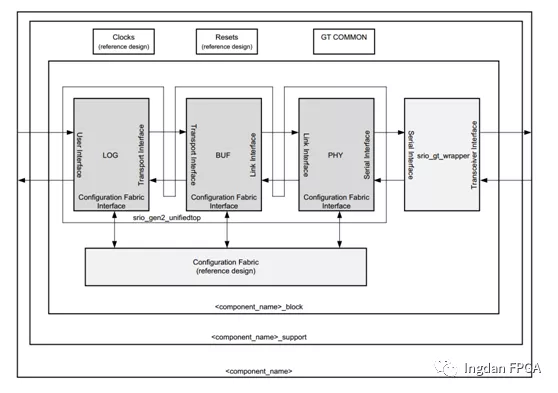

介绍 本处将从SRIO的数据流,数据协议,常用FPGA支持模式,以及IP例程中的时钟大小计算等部分介绍SRIO的情况。 3.1 SRIO的数据流 SRIO通过生成IP后

2024-12-10 16:24

FPGA(现场可编程门阵列)和DSP(数字信号处理器)之间通过SRIO接口进行调试通常需要以下步骤。

2024-04-19 11:48

本帖最后由 一只耳朵怪 于 2018-6-25 14:57 编辑 请问在使用ddr3 和srio接口时,其外部时钟(ddr3clk和sriosgmiiclk)是必须的吗,考虑到其内部有专门的sysclk与之对应。另外ddr3

2018-06-25 06:37

IP CORE SRIO 2.1 ENDPOINT ECP3

2023-03-30 12:02

请问C6678 hypelink SPICE 仿真模型哪里可以找到

2018-06-21 18:11