GIC硬件原理 ARM公司提供了一个通用的中断控制器 GIC(Generic Interrupt Controller) , GIC 的版本包括 V1 ~ V4 ,由于本人使用的SoC中的中断控制器

2023-09-28 14:58

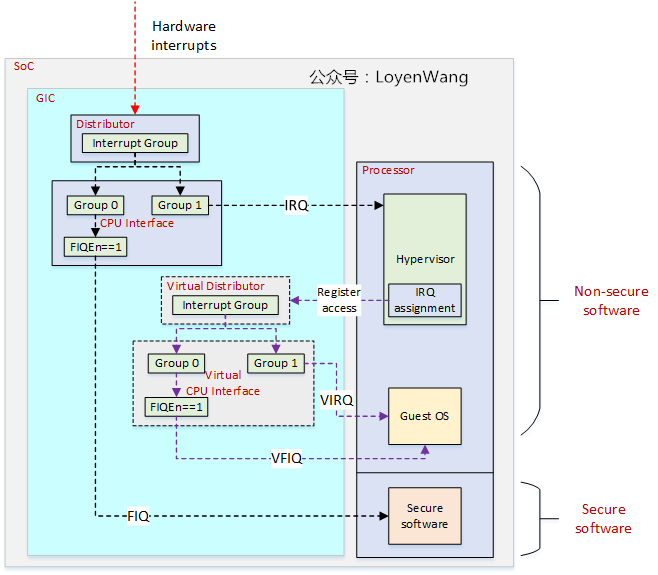

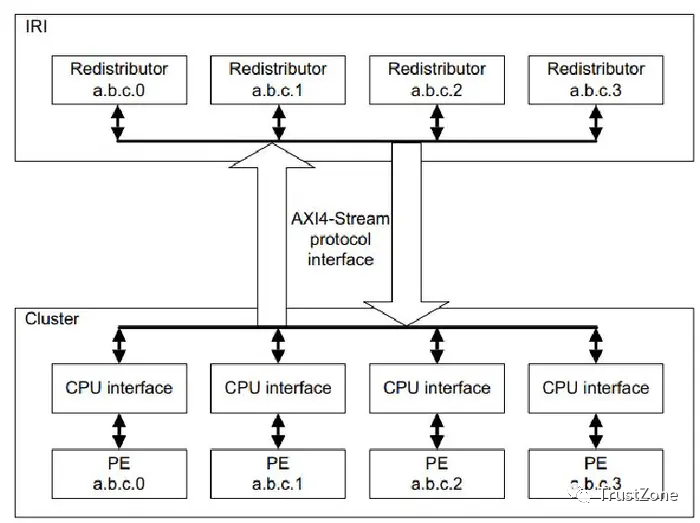

• ◾nVIRQ: 虚拟普通中断 • ◾nVFIQ: 虚拟快速中断 (2)gicv3和ARM Core的连接 gicv3 AXI-stream协议 • ◾gic stream协议,是基于AXI-stream协议

2023-11-07 18:07

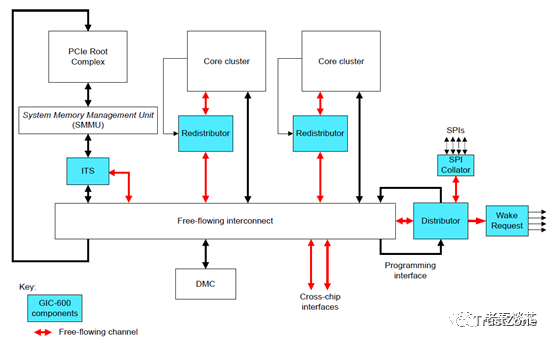

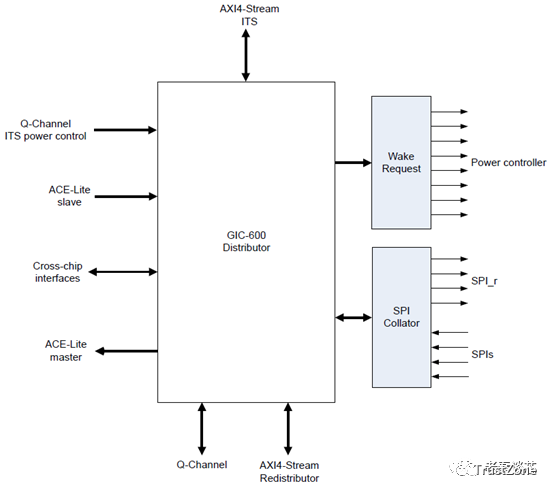

为了适应大规模的SoC设计,GIC-600被设计成分布式IP。 所谓分布式,GIC-600由几种组件构成,每个组件可以跟其它相关模块在物理设计上摆放在一起,并与其拥有共同的电源域;组件之间通过片上网

2023-11-07 17:19

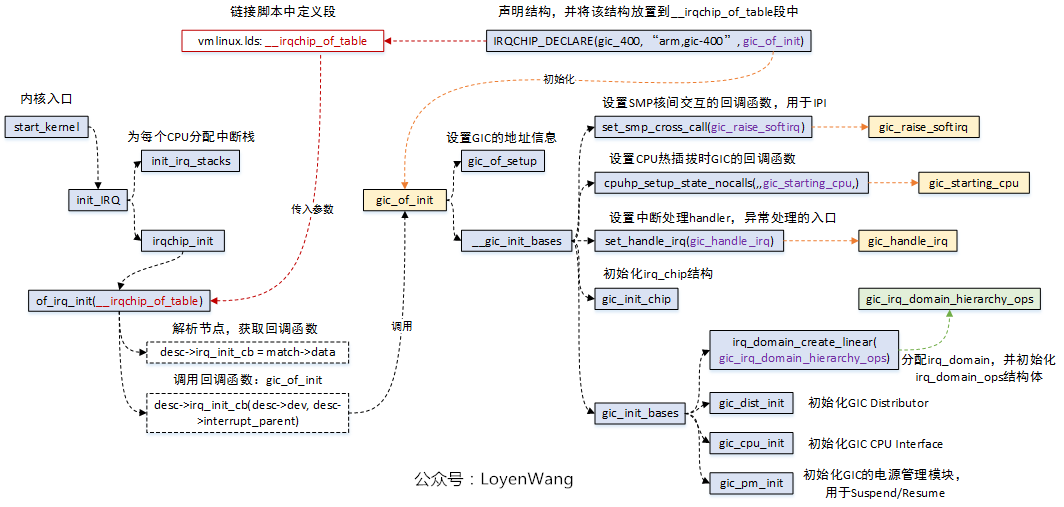

驱动流程分析 GIC驱动的执行流程如下图所示: 首先需要了解一下链接脚本 vmlinux.lds ,脚本中定义了一个 __irqchip_of_table 段,该段用于存放中断控制器信息,用于最终来

2023-09-28 15:09

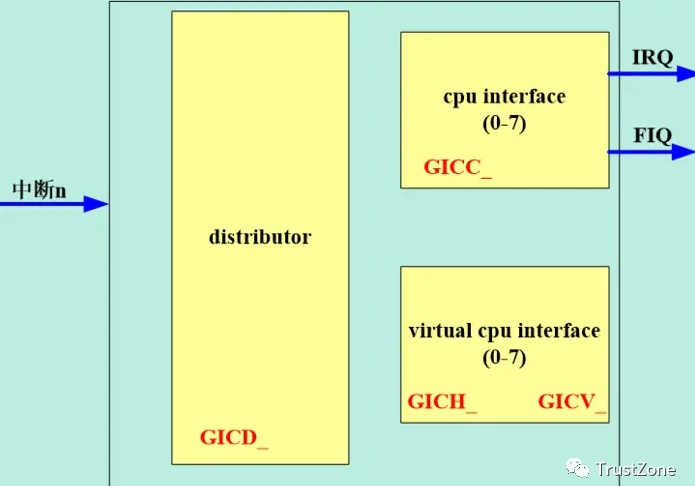

的,根据配置决定中断发往的core。最后选择最高优先级中断发送给cpu interface。寄存器使用 GICD_ 作为前缀。一个gic中,只有一个GICD。 • cpu interface:将

2023-11-08 15:57

接下来看看每个组件。 • 首先是distributor,一个SoC只有一个。 •它的组件只能与distributor通信。所以,可以看出,distributor是GIC-600中的核心,其作用是收集

2023-11-07 17:29

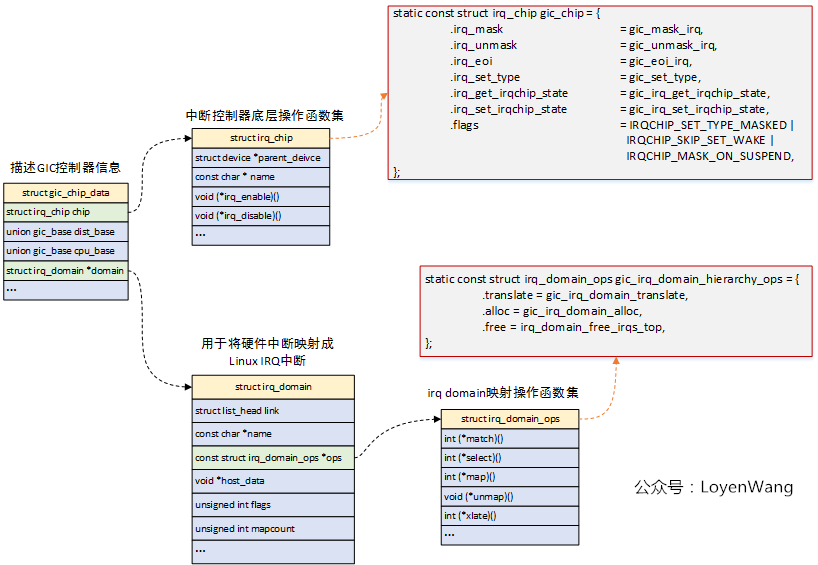

数据结构分析 先来张图: GIC驱动中,使用 struct gic_chip_data 结构体来描述GIC控制器的信息,整个驱动都是围绕着该结构体的初始化,驱动中将函数指针都初始化好,实际的工作

2023-09-28 15:18

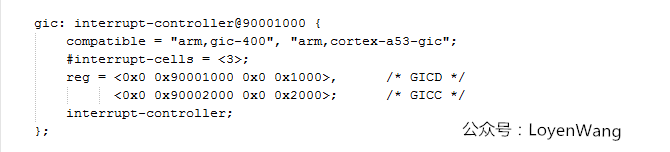

字段:用于与具体的驱动来进行匹配,比如图片中arm, gic-400,可以根据这个名字去匹配对应的驱动程序; interrupt-cells字段:用于指定编码一个中断源所需要的单元个数,这个值为3

2023-09-28 15:03

为了适应大规模的SoC设计,GIC-600被设计成分布式IP。所谓分布式,GIC-600由几种组件构成,每个组件可以跟其它相关模块在物理设计上摆放在一起,并与其拥有共同的电源域

2023-02-06 11:36

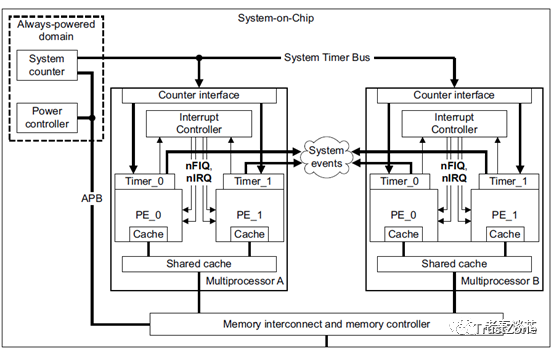

跟distributor连接的部分就不说了。Cpu_active是指示cluster或core的状态,可以用于idle管理。ppi_id用于多核设计时,区分每个redistributor。PPIs就是PPI中断线 从上面可以看出来,所谓的“私有”是说这些中断信号是core专有的。对于PPI,ARMv8定义了三种规格,8,12和16。所以对于不同的core来说,可能PPI数量不一样。 上面是ARMv8-A的架构spec里,关于timer的图。我们可以看到,core的timer会发PPI,而中断控制器返回FIQ或者IRQ给core。细心的同学可能会问了,在redistributor上面

2023-11-07 17:38