我在2015年底到2016年初的时候,使用7 Series FPGA Transceivers完成了TS流数据的传输,当时使用的传输速度为3.125G,SerDes选取的是8b/10b编码方式

2020-12-30 17:24

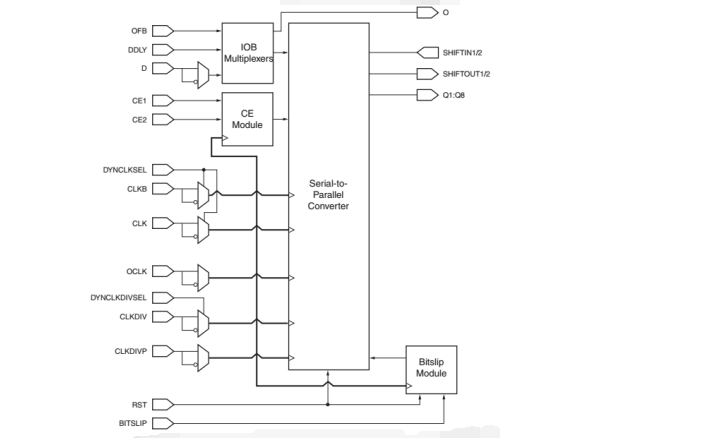

因为摄像头输出的LVDS信号速率会达到600Mbps,我们将不能够通过FPGA的I/O接口直接去读取这么高速率的信号。因此,需要使用Xilinx FPGA内的SerDes去实现高速数据的串并转换。

2020-12-30 17:24

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。从PCI到PCI Express, 从ATA到SATA,从并行ADC接口到JESD204, 从RIO

2021-07-28 07:02

开拓者FPGA DEVB_121X160MM 6~24V

2023-03-28 13:06

新起点FPGA DEVB_90X128MM 6~24V

2023-03-28 13:06

赛灵思 Artix-7 FPGA 是业界唯一的在低端器件上整合了高速收发器的方案,该方案提供了自适应均衡、2D 眼图以及IBIS-AMI仿真模型来简化针对成本敏感型应用的高速串行设计,观看视频,4分钟教您搞定高速SerDes端口设计。

2016-07-27 17:29

用户在产品选型和方案设计之初,对于硬件接口资源分配不熟悉,不遵守芯片规范使用导致项目出现问题,造成了严重损失。本期我们就此系列平台的SerDes资源分配做一篇文章。LS系列产品的资源不可为不丰富,其中最让人头晕的当属于SerDes协议。百度百科这样解释,

2021-12-20 06:01

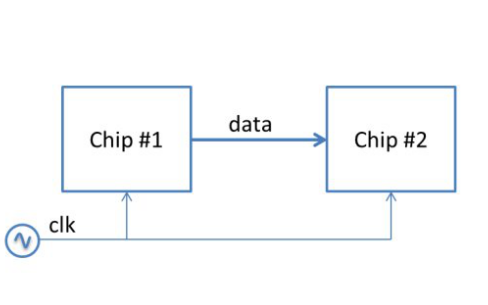

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。a)、时钟...

2021-07-28 08:35

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中

2021-07-26 07:33

SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 应对未来高速

2021-11-12 06:46