先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在

2020-03-29 17:19

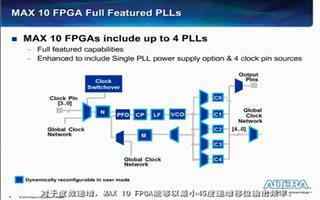

MAX 10 FPGA PLL和时钟培训,此次培训涉及到器件系列的时钟特性和选项。有20个全局时钟网络,全局CLK输入引脚数量也可以加倍,用作通用IO引脚。并且采用动态用户控制进行各种选择和电源控制,构建鲁棒的时钟网络源。它所有4个

2018-06-20 08:00

现今的FPGA设计大多采用时序逻辑,需要时钟网络才能工作,通常情况下,时钟通过外部晶体振荡器产生。虽然大多数情况下使用外部晶振是最好的选择。然而,石英晶振对温度漂移敏感

2012-11-19 17:07

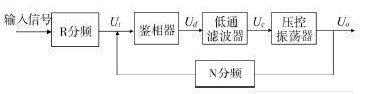

频率合成器主要有直接式、锁相式、直接数字式和混合式4种。目前,锁相式和数字式容易实现系列化、小型化、模块化和工程化,性能也越来越好,已逐步成为最为典型和广泛的应用频率合成器[1]。本文主要采用集成锁相环PLLphase-Lockde Loop芯片CD4046,运用FPGA来实现

2019-01-07 09:52

熟悉 HME FPGA PLL IP 的使用,实现 LED 流水灯功能。

2023-05-30 10:04

用FPGA的锁相环PLL给外围芯片提供时钟 FPGA锁相环PLL(Phase-Locked Loop)是一种广泛使用的时钟管理电路,可以对输入时钟信号进行精确控制和提高

2023-09-02 15:12

随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得到广泛应用,本文将深入探讨PLL技术在

2025-06-20 11:51

PLL(phase-locked loop),即锁相环。是FPGA中的重要资源。由于一个复杂的FPGA系统往往需要多个不同频率,相位的时钟信号。所以,一个FPGA芯片中

2021-01-22 09:41

易灵思的FPGA在生成PLL的方式与别的厂家稍有区别,这与其的core和interface架构是相对应的。对于易灵思的FPGA来讲,PLL,GPIO,MIPI,LVDS

2025-06-07 16:18

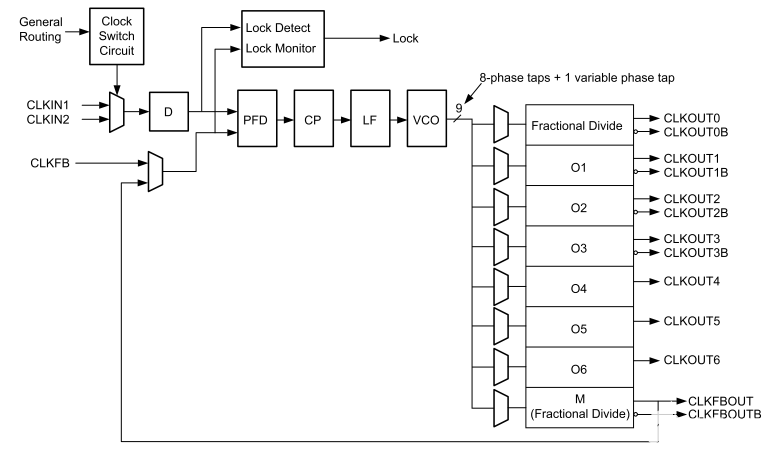

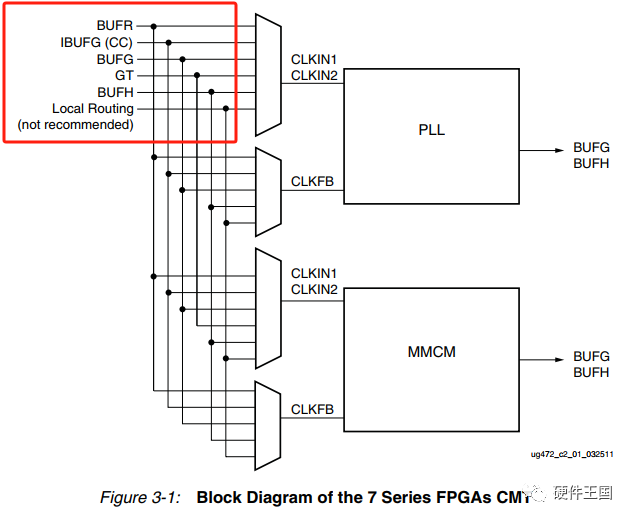

7系列FPGA包含最多24个CMT块,CMT具体的分布和与其他时钟资源的关系请参考本合集(FPGA应用开发)的上一篇文章。本文主要介绍CMT内部MMCM和PLL的区别以及在实际开发中怎么使用CMT,怎么实现跨时钟区域

2023-11-17 17:08