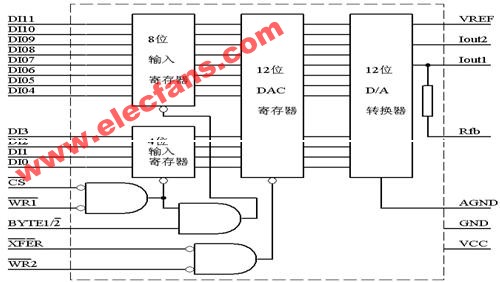

DAC1210结构框图及引脚说明:图4.14 DAC1210原理框图

2009-01-14 12:58

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本

2022-04-21 08:55

你好。我想知道 DAC 引脚能够提供多少电流。STM32G081 数据表指示“任何 I/O 和控制引脚提供的输出电流 = 15mA”。这个 15mA 也是 DAC 源极

2023-01-10 06:26

FPGA设计中DAC控制的Verilog实现(单片机电源维修)-该文档为FPGA设计中DAC控制的Verilog实现资料,讲解的还不错,感兴趣的可以下载看看………………

2021-07-26 12:18

FPGA的引脚交换

2020-01-20 17:53

。我们从时钟发生器的不同端口提供FPGA,ADC和DAC。 ADC接口以源同步模式运行,数据相对于DCO信号锁存,来自ADC和数据。在FPGA内部,我们使用FIFO交叉时钟域。到目前为止ADC部分还不

2020-03-12 11:12

怎么实现基于FPGA的dac控制?

2021-11-02 07:32

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本

2025-03-14 13:54

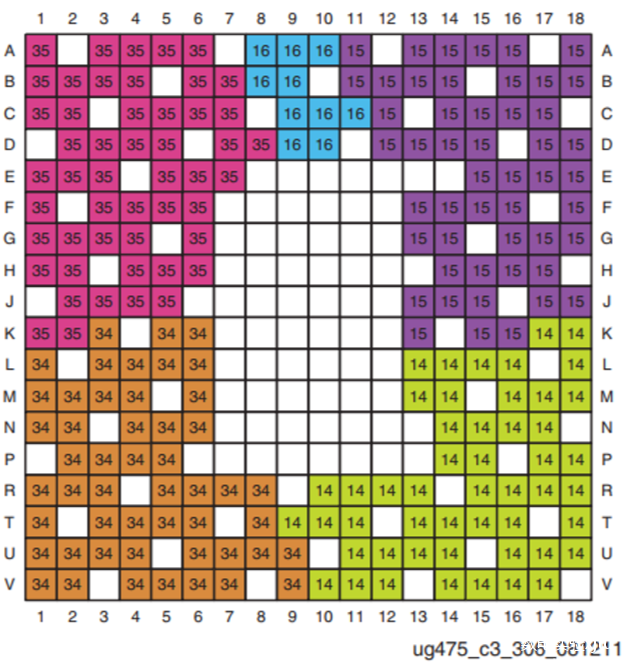

FPGA的引脚排布在芯片背面,以EGO1板载芯片XC7A35T-1CSG324C 为例,下图中每个小格代表一个引脚,共有18行18列,共324个引脚。

2023-09-17 15:09