,被赋值对象会比赋值对象差一个时钟周期。 有了上述理解之后,我们就很容易明白为什么阻塞

2017-09-19 18:32

长延时周期定时器 这里提供的由一个555

2009-10-09 15:40

FPGA在一个时钟周期可以读取多个RAM数据吗?如何理解FPGA中存放程序的RAM?

2023-10-18 15:28

对于VerilogHDL语言中,经常在always模块中,面临两种赋值方式:阻塞赋值和非阻塞赋值。对于初学者,往往非常迷惑这两种赋值方式的用法,本章节主要介绍这两种文章

2020-01-30 17:41

今天给大家普及一下阻塞赋值和非阻塞赋值的相关知识

2023-07-07 14:15

在FPGA设计中我们经常会遇到对一个信号进行延时的情况,一般只延时

2022-06-30 17:39

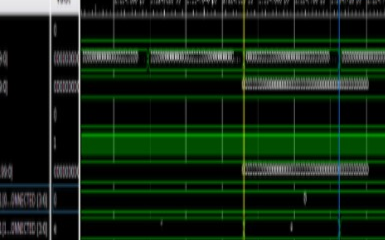

设计背景: 阻塞 (=)和非阻塞(=)一直是在我们FPGA中讨论的问题,资深的学者都是讨论的是赋值应该发生在上升下降沿还是在哪里,我们在仿真中看的可能是上升下降是准确的,但是在时间电路中这就

2018-05-31 11:40

采用FPGA的CARRY4进位单元,每个CARRY4的COUT连接到下一个CARRY4的CIN,这样级联起来,形成延时链;每个COUT做为抽头输出到触发器,通过本地时钟进行数据采样。假定每个

2022-02-16 16:21

”=“阻塞赋值与”<=“非阻塞赋值是verilog语言中的两种不同的赋值方式,下面将对两种赋值方式进行比较。方便进行理解和使用。

2023-09-12 09:06

使用逻辑门和连续赋值对电路建模,是相对详细的描述硬件的方法。使用过程块可以从更高层次的角度描述一个系统,称作行为级建模(behavirol modeling)。 1. 过程赋值

2023-03-17 21:50