本篇将详细介绍如何利用Verilog HDL在FPGA上实现SRAM的读写测试。SRAM是一种非易失性存储器,具有高速读取和写入的特点。在FPGA中实现SRAM读写测试

2025-10-22 17:21

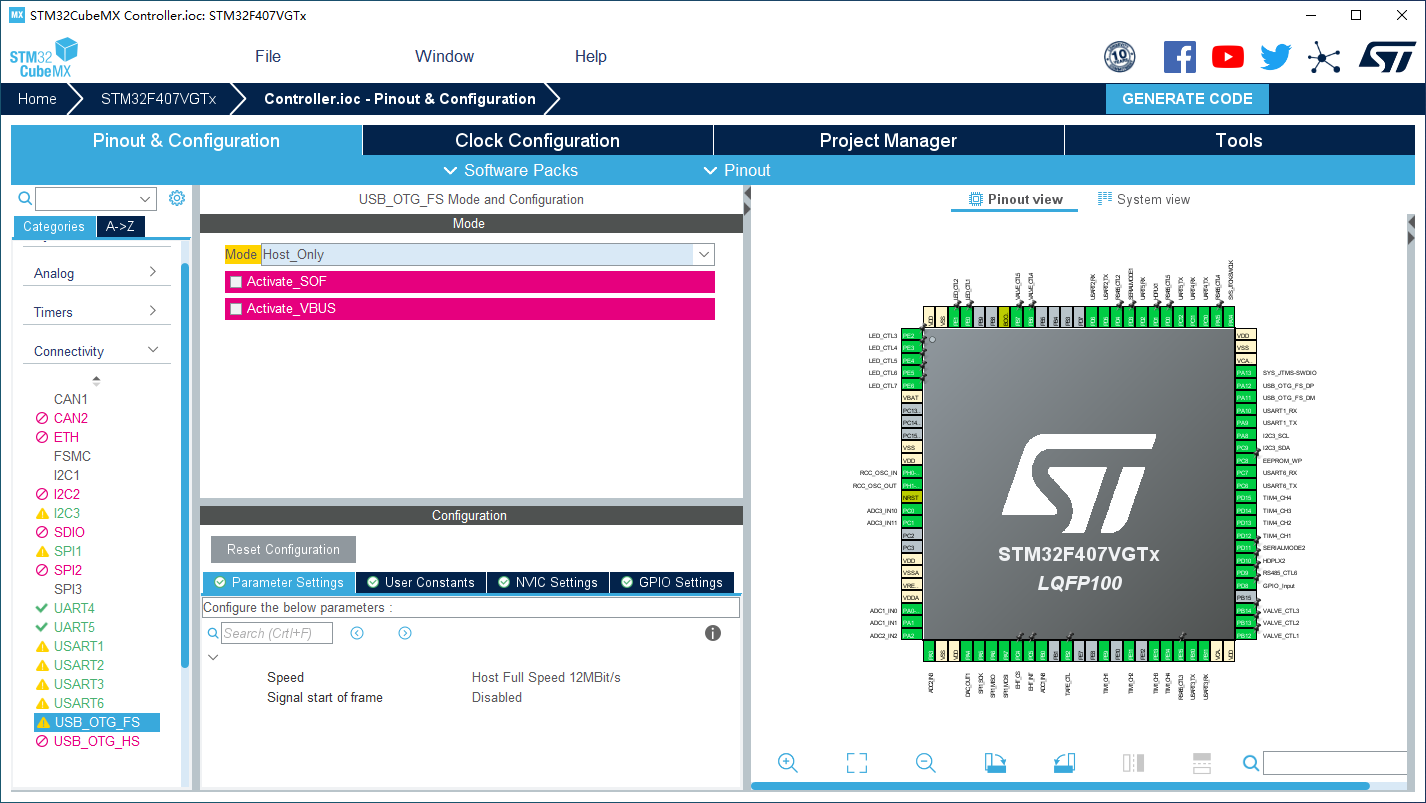

在项目应用中,经常会有对外交换数据的需求。USB接口读写U盘无疑是一种颇为方便的选择。在这一篇中,我们就来讨论如何在STM32上实现USB主机读写U盘文件的方法。

2022-12-13 17:20

本设计在基于Xilinx Virtex-6 FPGA内嵌PCI Express Core的基础上,实现了由PCI Express板卡主动发起的DMA读写,可完成PC和PCI Express板卡之间

2017-11-18 10:26

STM32 通过 FSMC 读写CPLD 的程序,CPLD挂在STM32的地址线和数据线上,将CPLD看做片外RAM的方式来进行读写,在我做的板子上CPLD挂在第四个区

2018-04-20 10:38

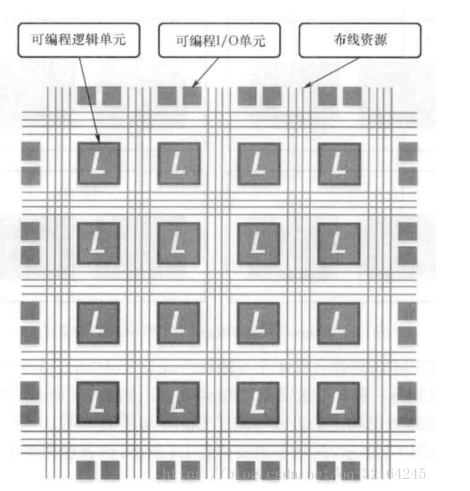

FPGA中的基本逻辑单元是CLB模块,一个CLB模块一般包含若干个基本的查找表、寄存器和多路选择器资源,因此FPGA中的逻辑表达式基于LUT的。

2018-07-28 09:58

本文主要介绍了一种基于STM32+FPGA的数据采集系统的设计与实现,利用STM32硬件中的FSMC、ETHERNETMAC、定时器等外设功能,以及FPGA灵活的逻辑可操控性,解决了系统接口

2017-12-23 15:43

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR3

2017-11-18 18:51

异步 FIFO 读写分别采用相互异步的不同时钟。在现代集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟,多时钟域带来的一个问题就是,如何设计异步时钟之间的接口电路。异步 FIFO

2020-07-16 17:41

本文主要介绍了一种基于STM32+FPGA的全彩LED显示屏系统的设计,STM32作为主控芯片,通过以太网传输数据,以FLASH作为存储模块,由FPGA完成对LED显示屏的高速扫描刷新。系统工作

2017-12-28 13:59

闪存随机读写与连续读写各有其重要性,具体取决于应用场景和需求。 随机读写的重要性 延迟小,响应快 : 闪存(尤其是SSD)的随机读写性能通常较强,因为其延迟小且没有机械

2024-10-12 11:44