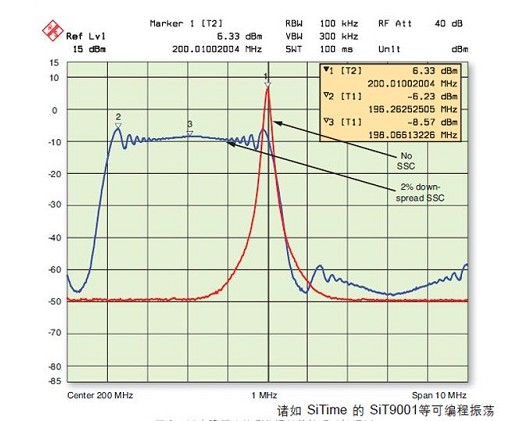

从图中可以看出,该斩波波形是较差的。在FPGA系统中则会表现为:整个系统电流偏大,进而影响功耗偏大。

2020-05-05 06:26

通常来讲,“一个好汉三个帮”,一个完整的嵌入式系统中由单独一个FPGA使用的情况较少。##系统架构确定,下一步就是FPGA与各组成器件之间互联的问题了。

2015-05-12 13:41

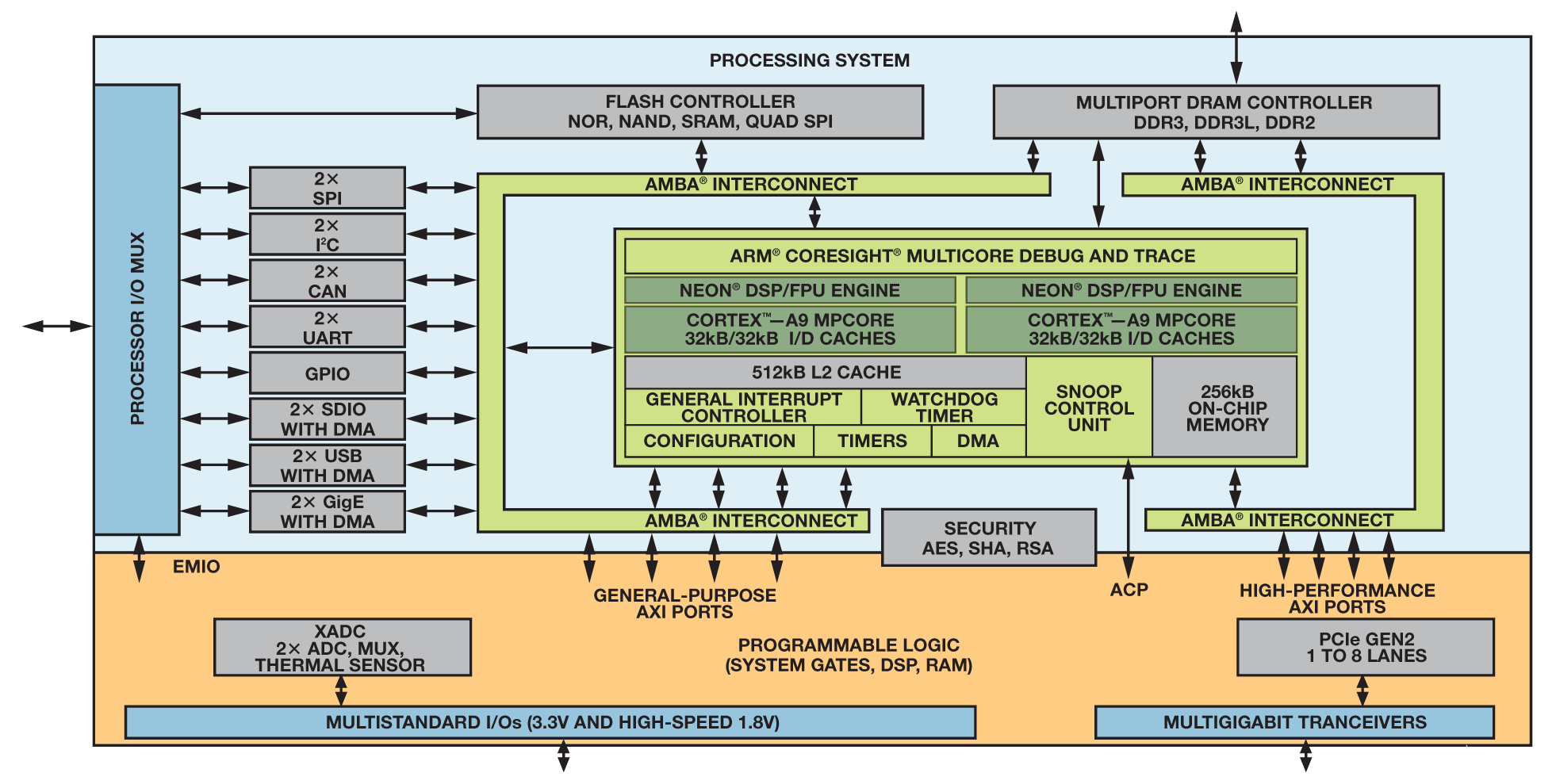

标,但实际上在印刷电路板上设计 FPGA 的硬件级工作也会出现很多有趣的挑战,只有解决了这些挑战才能实现成功设计。 一切的起点均在于架构。硬件开发第一步就是定义解决方案的架构。架构应该对应于系统要求,并具体明确它们如何在硬件中得到实现。

2018-01-12 11:49

,因此它们需要额外的处理能力来实时执行所有任务。多芯片架构通常用于实现现代电机控制系统:数字信号处理器(DSP)执行电机控制算法,FPGA实现高速I/O和网络协议,微处理器处理执行控制。

2023-01-09 15:27

内在可编程的硅 MEMS 时钟振荡器架构能够帮助采用 FPGA 的系统设计人员解决许多难题。这种微型机电系统架构能够轻松整合一些其它功能,如:用于消减 EMI 的扩频时钟、用于消除抖动的数控振荡器以及高速应用中的失效

2013-08-15 11:12

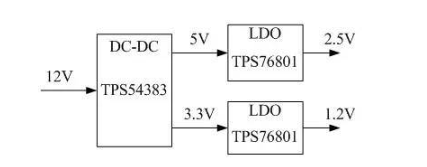

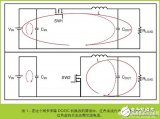

为了提高转换效率,FPGA 系统的设计人员正在放弃使用线性调节器,转而采用开关式 DC/DC转换器。虽然开关式DC/DC 转换器可以显著提高效率,但设计复杂性也会相应提高,同时还会增加器件数量和封装尺寸。对于高速 I/O 而言,最重要的问题在于开关式 DC/DC

2018-07-19 14:56

随着FPGA制造工艺尺寸持续缩小、设计配置更加灵活,以及采用FPGA的系统的不断发展,原来只采用微处理器和ASIC的应用现在也可以用FPGA来实 现了。最近

2018-07-13 09:19

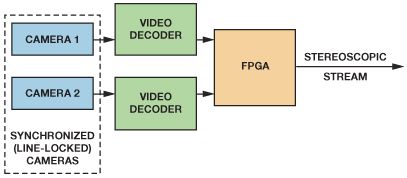

本文概述了使用模拟或HDMI摄像机实现立体视觉(3D视频)的要求。它描述了一个基于 FPGA 的系统,该系统将两个视频流组合成一个 3D 视频流,以便通过 HDMI 1.4 发射器传输,以及一个

2023-02-02 15:09

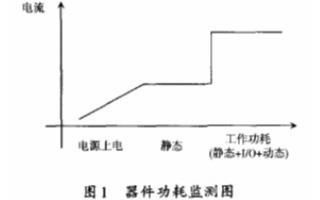

功耗一般由两部分组成:静态功耗和动态功耗。静态功耗也称为待机功耗,是指逻辑门没有开关活动时的功率消耗,主要是由晶体管的漏电流引起,由源极到漏极的漏电流以及栅极到衬底的漏电流组成,图1中静态部分显示了器件的静态功耗。图中最后阶段显示的是器件正常工作时的功耗,工作功耗同时包括静态功耗,I/O以及动态功耗。

2020-01-16 09:46

在复位电路中,由于复位信号是异步的,因此,有些设计采用同步复位电路进行复位,并且绝大多数资料对于同步复位电路都认为不会发生亚稳态,其实不然,同步电路也会发生亚稳态,只是几率小于异步复位电路。

2020-06-26 16:37