FPGA程序的固化,即掉电后再上电,程序仍能正常运行。

2023-07-19 16:41

本文以提高FPGA远程更新程序的方便性为目标,提出了一种基于EPCS Flash的远程在线更新FPGA程序的方法,从而在应用中能够使基于

2012-02-22 11:33

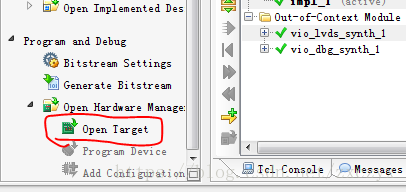

在使用Vivado 的SDK进行在线调试时,需要将FPGA的bit文件烧写到FPGA中,但是在使用SDK烧写程序之前必须将已经固化在FPGA的

2020-11-23 16:00

Xilinx zynq系列FPGA实现神经网络评估 本篇目录 1. 内存占用 1.1 FPGA程序中内存的实现方式 1.2 Zynq的BRAM内存大小 1.3 一个

2022-07-10 09:24

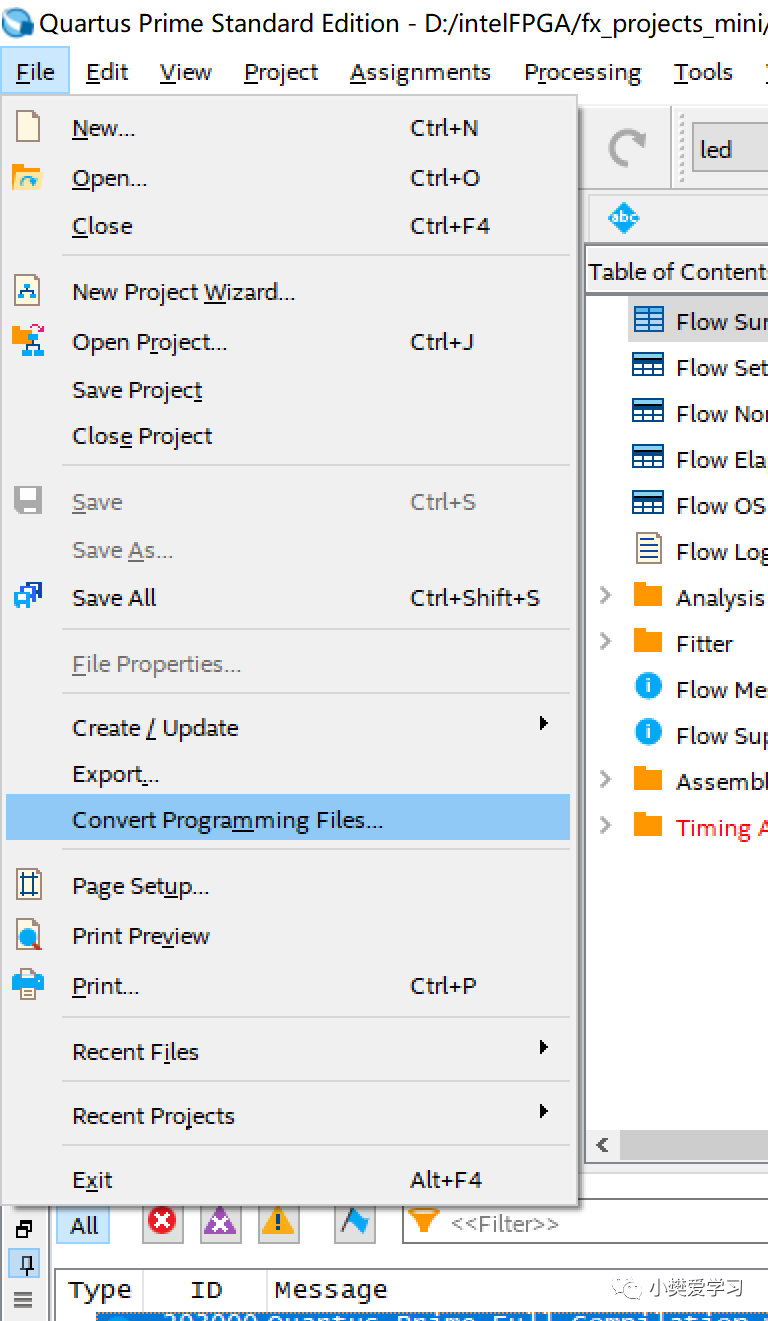

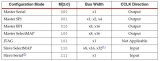

1. Master Modes 自动下载FPGA程序在本地的非易失性存储器,而且主模式的时钟来自内部晶振。 2. Slave Modes 外部控制下载FPGA配置模式,通常称为从模式,有串行

2021-05-11 15:22

对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读

2022-02-16 16:21

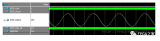

DDS 同 DSP(数字信号处理)一样,是一项关键的数字化技术。DDS 是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。与传统的频率合成器相比,DDS 具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

2023-10-31 11:14

本课程前期是基础理论的讲解,后期是结合经验和项目实践提炼的主要内容,围绕抗干扰和工程实现进行原理阐述,省去了复杂的公式推导过程,和大家分享硬件学习经验。

2019-11-08 07:02

在系统上电时,需要从外部载入所要运行的程序,此过程被称为程序加载。多数情况下,从外部专用的 读入程序。这种方式速度慢,而且只能加载固定的程序。显然,当系统需要容量大而且

2019-03-22 16:20

时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。

2022-12-05 09:39