FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA

2023-06-26 14:42

在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束。但在复杂电路中,为了减少系统中各部分延时,使系统协同工作,提高运行频率,需要进行时序约束。通

2018-03-30 13:42

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA

2023-06-06 17:53

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序

2023-06-12 17:29

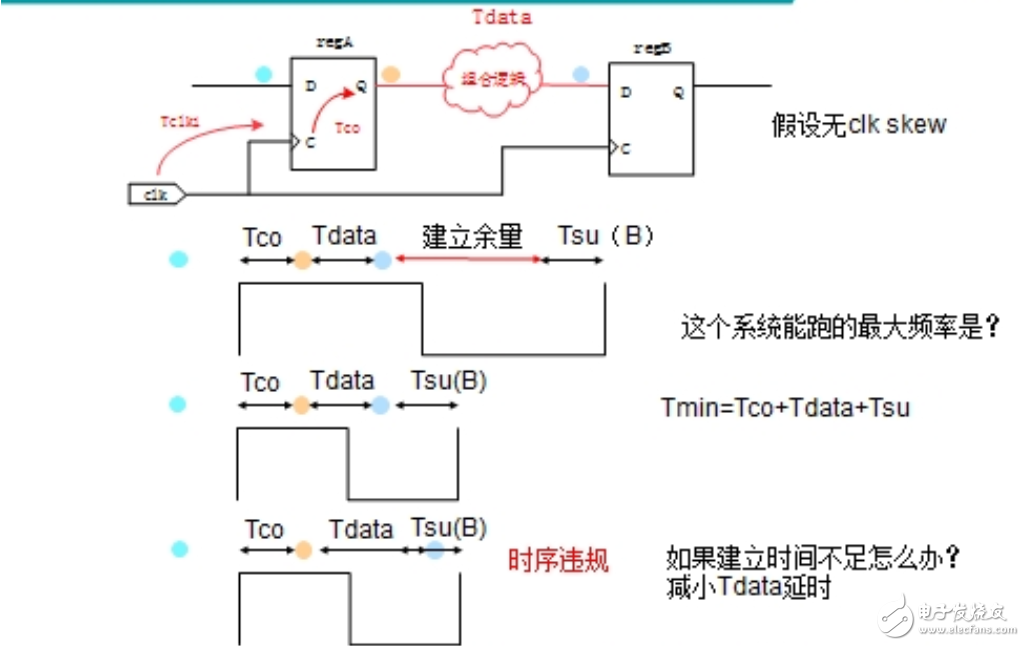

A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移

2021-09-30 15:17

FPGA在与外部器件打交道时,端口如果为输入则与input delay约束相关,如果最为输出则output delay,这两种约束的值究竟是什么涵义,在下文中我也会重点刨析,但是前提是需要理解图1和图2建立余量和保持

2019-11-10 10:06

STA(Static Timing Analysis,即静态时序分析)在实际FPGA设计过程中的重要性是不言而喻的

2023-06-26 09:01

现有一块ADC连接到FPGA上,需要在FPGA上实现高速数据的读取,那么第一步自然就是完成可靠的硬件连线

2023-06-28 09:07

前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束

2023-06-12 17:33