FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21

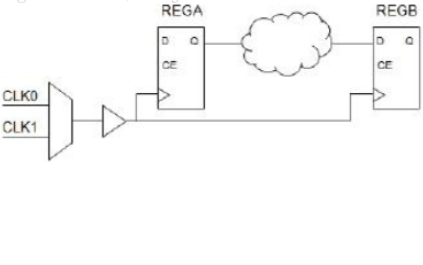

说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束

2021-01-11 17:46

本篇文章用于总结之前学习的time quest,并且我已经能够利用公式,计算出slack了,并能够根据setup slack来更改优化代码了。时光由隔了1个月,时序分析的路没有终点,本篇文章是对之前

2021-01-13 16:02

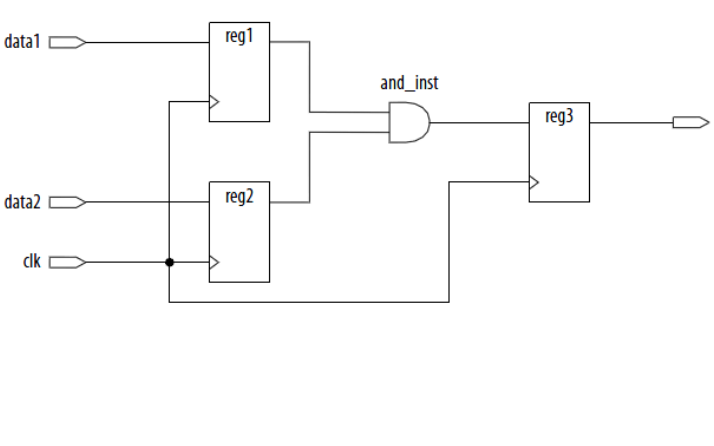

下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。我们的系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中

2021-01-11 17:44

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应

2021-01-11 17:44

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束。这一方面是由FPGA的

2021-01-12 17:31

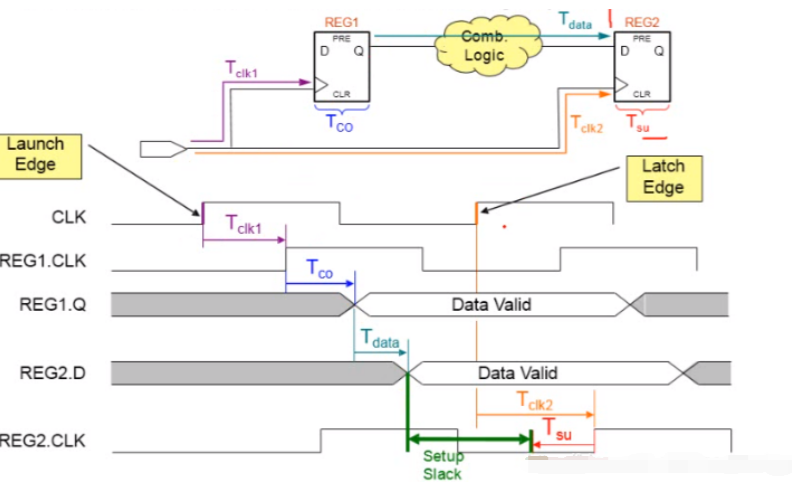

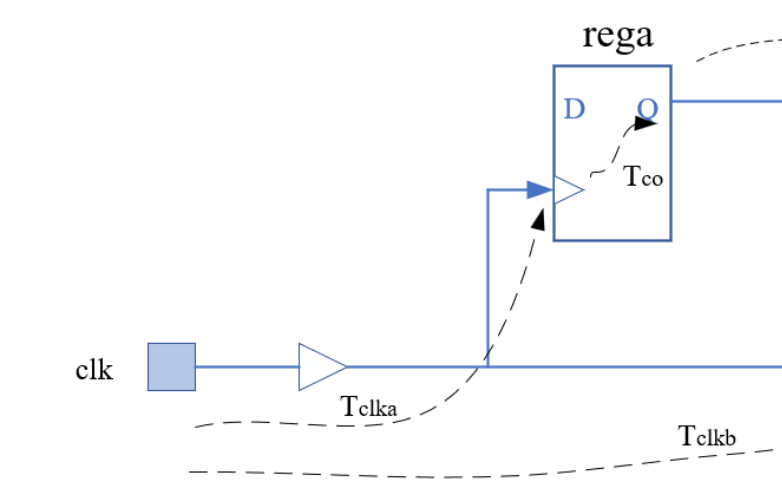

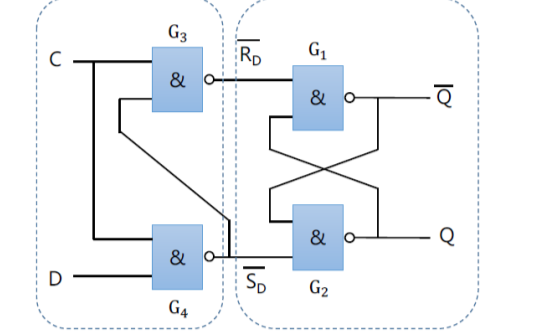

组合逻辑延迟和走线延迟。Tsu表示捕获寄存器建立时间要求。Th表示捕获寄存器保持时间要求。其中Tco、Tsu和Th是由FPGA的芯片工艺决定的。所以,我们所谓的时序约束,实际上就是对时钟延迟和Tdata做一定的要求或

2021-01-12 17:31

xilinx的Vivado工具也一直在更新,到本人记录此文的时候,Vivado已经有2017.3版本了,建议大家使用最新的Vivado工具。

2021-01-12 17:31

由于每次我都写了功能仿真过后,放到门级仿真,就出问题,而门级仿真通常对实际还是有一定的指导意义的,通常我只要门级仿真跑不出来,多半实际都没跑出来,而且门级仿真调试起来相当麻烦,所以功能仿真+时序约束+signal tap 才是最好的方法。

2021-01-13 16:02

首先,我们点进去都会叫我们选择一个模型,来建立网表,如果,我们选择slow,那么我们知道对setup slack自然会有影响更大,如果我们选择fast模型,就会对hold slack的模型影响更大。

2021-01-13 16:02