引脚和区域约束也就是LOC约束(location)。定义了模块端口和FPGA上的引脚的对应关系。 那么我们应该怎么写呢?

2018-07-14 02:49

引言:上一篇文章我们介绍了通过添加电阻器、场效应晶体管(FET)开关、电平转换器甚至其他Xilinx FPGA等选项实现HP Bank IO与2.5V/3.3V外设对接的方法。本文介绍利用TI公司TXS0108实现FPGA

2023-05-16 09:02

现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2017-05-18 10:51

: 了解通用外设标准接口层、外设硬件层开发、外设驱动层开发、外设用户配置文件开发。 图1 通用外设文

2022-05-31 17:28

对外设进行测试。以后还有一个很重要的自定义用户Ipcore设计,下个实验来做下这个(一开始以简单的led和sw为例)。这个实验就使用呢自带外设IP。

2017-02-09 14:23

现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2023-05-04 17:38

现在的FPGA向引脚分配信号的任务曾经很简单,现在也变得相当繁复。

2016-07-27 20:24

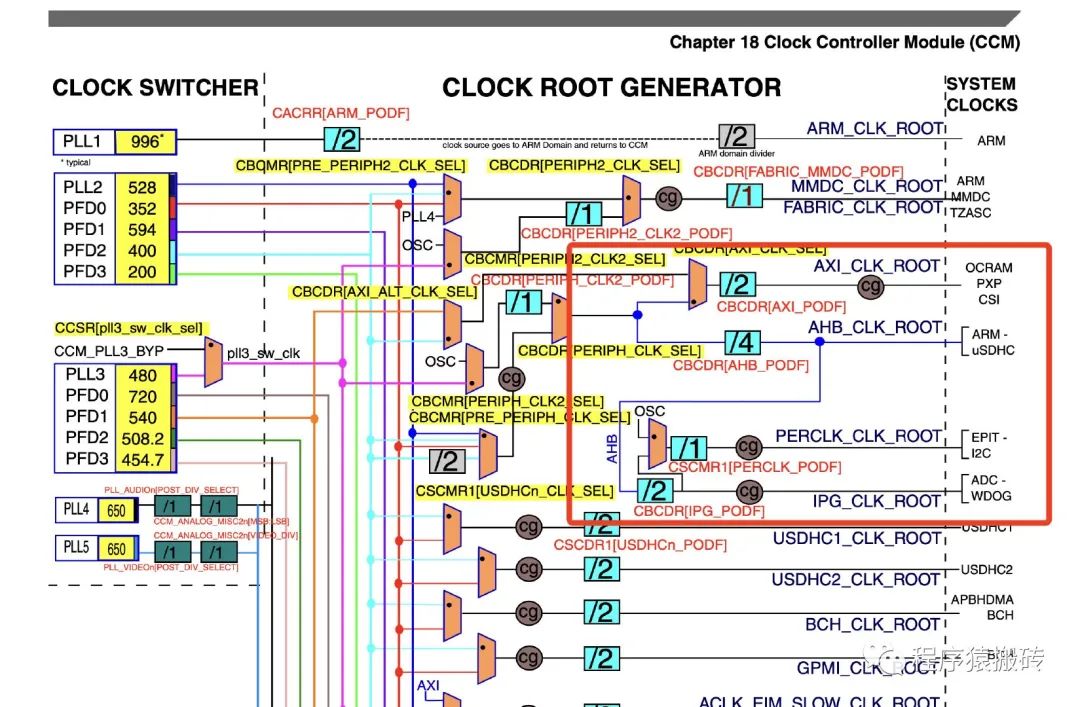

外设需要工作也需要时钟驱动,通过多路选择器以及对应的寄存器配置初始化最适合的外设频率可以让外设更高频的工作。

2023-03-02 16:22

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及

2020-10-10 09:25