一般情况下,FPGA器件内部的逻辑会在每个时钟周期的上升沿执行一次数据的输入和输出处理,而在两个时钟上升沿的空闲时间里,则可以用于执行各种各样复杂的处理。而一个比较耗时的复杂运算过程,往往无法一个时钟周期完成,便可以切割成几个耗时较小的运算,然后在数个时钟上升沿后

2018-05-23 05:56

lattice公司的iCE40系列是超低功耗非易式FPGA器件,查找表(LUT)从384到7680.此外还具有嵌入区RAM(EBR),非易失可配置存储器(NVCM)和锁相环(PLL),非常适用

2018-05-13 11:56

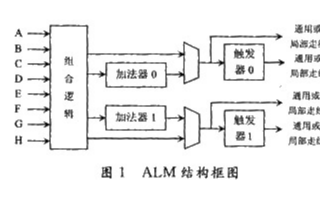

图2列出了和传统的4输入LUT结构的FPGA相比较,采用ALM的StratixⅡFPGA器件例化3输入加法器的优势。从图2中可以清楚地看出,对于同样3个2 b数据相加的逻辑结构,传统4输入LUT结构

2020-03-03 10:45

现场可编程门阵列(FPGA)的出现是超大规模集成电路(VLSI)技术和计算机辅助设计(CAD)技术发展的结果。FPGA器件具有集成度高、体积小、可以通过用户编程实现专门应用的特点。这些特点非常适合

2020-08-07 17:14

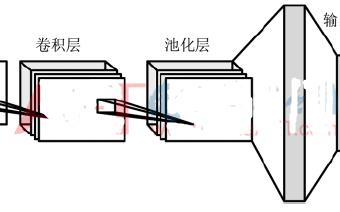

随着近些年深度学习的迅速发展和广泛的应用,卷积神经网络(CNN)已经成为检测和识别领域最好的方法,它可以自动地从数据集中学习提取特征,而且网络层数越多,提取的特征越有全局性。通过局部连接和权值共享可以提高模型的泛化能力,大幅度提高了识别分类的精度。并且随着物联网的发展,部署嵌入式端的卷积神经网络要处理大量的数据,这将会消耗大量的资源与能量,而嵌入式设备通常用电池维持工作,频繁更换电池将会提高成本,因此对于推断阶段的运算加速以及低功耗设计有重要实际意义。

2020-07-15 21:00

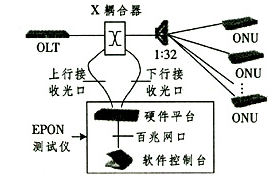

EPON采用单纤双向通信方式,为了观测EPON的内部运行情况,我们在OLT与光分配网络(ODN)主干光纤之间接入X型光耦合器,分出部分上行和下行光信号至EPON测试仪,以实现对上下行链路的监视,如图1所示。

2021-06-17 14:57

异步 FIFO 读写分别采用相互异步的不同时钟。在现代集成电路芯片中,随着设计规模的不断扩大,一个系统中往往含有数个时钟,多时钟域带来的一个问题就是,如何设计异步时钟之间的接口电路。异步 FIFO 是这个问题的一种简便、快捷的解决方案,使用异步 FIFO 可以在两个不同时钟系统之间快速而方便地传输实时数据。

2020-07-16 17:41

电路加速等领域应用广泛。随着微电子工艺技术的进步,FPGA器件向集成更多资源、更高速度及片上系统方向发展。FPGA器件内部具有丰富的可编程逻辑资源、输入输出口资源、锁相

2018-10-21 10:32

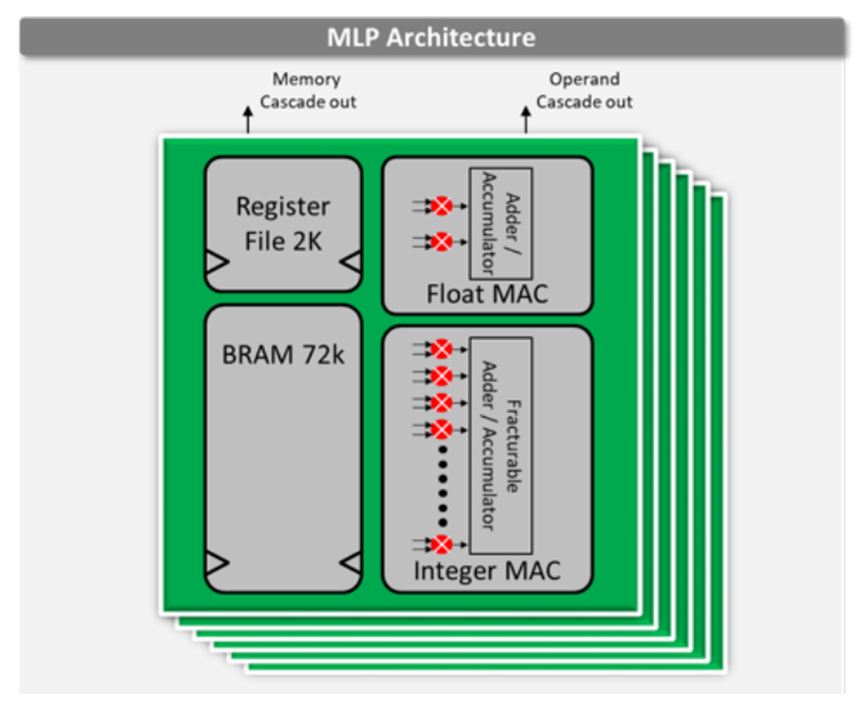

Achronix半导体公司推出了为AI优化的Speedster7t系列FPGA芯片,该系列包含专门针对AI工作负载的强化计算引擎。随着AI在各个领域变得普遍,在FPGA芯片上部署AI应用的需求促使了

2024-09-18 16:10

对于基于数字信号处理器(DSP)的设计,如果DSP没有足够的安全能力,便特别容易受到入侵。在许多应用中,如果使用FPGA以作配合来卸载DSP的部分工作,便可以轻易实施先进的安全功能。而且,如果配合

2018-10-09 16:58