前言:TSMaster目前有两种读取报文的模式:回调函数模式和fifo模式。fifo函数是TSMaster近期新增的函数,本文将重点介绍fifo模块。关于回调函数的使用

2025-03-14 20:04 上海同星智能科技有限公司 企业号

在STM32微控制器中,Boot引脚(通常指的是BOOT0和BOOT1引脚)的状态决定了设备启动时的引导模式。这些引脚的状态在复位时被读取,并据此选择启动哪块存储器。比如,STM32F103系列

2024-08-22 09:48

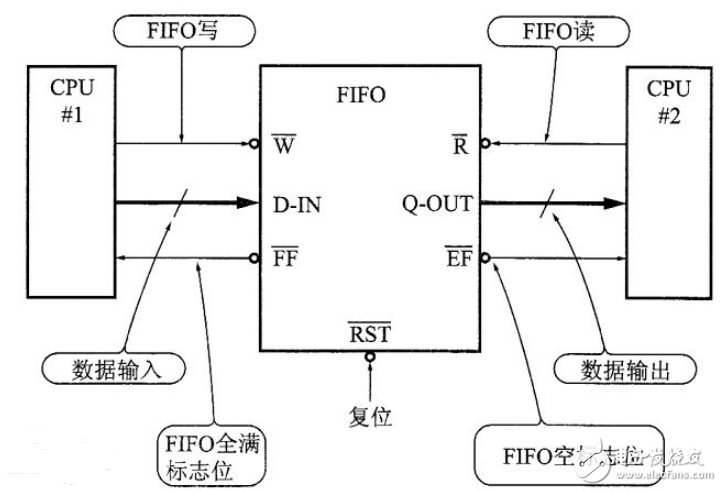

本文主要介绍了fifo存储器芯片型号有哪些?FIFO存储器是系统的缓冲环节,如果没有FIFO存储器,整个系统就不可能正常工作,它主要有几方面的功能:1)对连续的数据流进

2018-04-08 16:11

FIFO( First In First Out)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。作为一种新型大规模集成电路,

2017-12-06 14:29

1. FIFO简介 FIFO是一种先进先出数据缓存器,它与普通存储器的区别是没有外部读写地址线,使用起来非常简单,缺点是只能顺序读写,而不能随机读写。 2. 使用场景 数据缓冲:也就是数据写入过快

2024-06-04 14:27

情况下总是有效的,因此可在任意时间被读取。rd信号实际上就像“remove”信号;当其被插入的时候,FIFO缓存的第一个项(即head)被移除,下一个项变为可用项。

2023-09-11 10:12

FIFO(First In First Out)是异步数据传输时经常使用的存储器。该存储器的特点是数据先进先出(后进后出)。其实,多位宽数据的异步传输问题,无论是从快时钟到慢时钟域,还是从慢时钟到快时钟域,都可以使用 FIFO 处理。

2023-03-26 16:00

FIFO为什么不能正常工作?复位信号有效长度不够,接口时序不匹配,可看下面这篇文章。 本文将介绍: 非DFX工程如何确保异步FIFO自带的set_max_delay生效? DFX工程如何确保异步

2023-11-02 09:25

问题的有效方法。异步FIFO是一种在电子系统中得到广泛应用的器件,多数情况下它都是以一个独立芯片的方式在系统中应用。本文介绍一种充分利用FPGA内部的RAM资源,在FPGA内部实现异步FIFO模块的设计方法。这种异步

2020-07-21 17:09

FIFO的使用非常广泛,一般用于不同时钟域之间的数据传输,或者用于不同数据宽度之间的数据匹配。在实际的工程应用,可以根据需要自己写FIFO。不考虑资源的情况下,也可以使用Xilinx提供的IP核来完成。

2022-08-14 10:49