ADF4155结合外部环路滤波器、外部压控振荡器(VCO)和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。 ADF4155能够与外部VCO器件配合使用,工作频率高达8 GHz。 高

2025-04-25 14:15

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输

2020-03-29 17:19

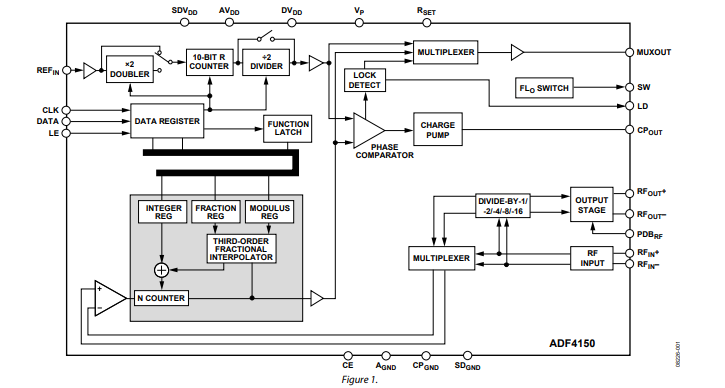

ADF4150结合外部电压控制振荡器(VCO)、环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。 它能够与外部VCO器件配合使用,且与ADF4350软件

2025-04-25 17:10

ADF4151结合外部电压控制振荡器(VCO)、环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。 它能够与外部VCO器件配合使用,且与ADF4350尺寸

2025-04-25 15:15

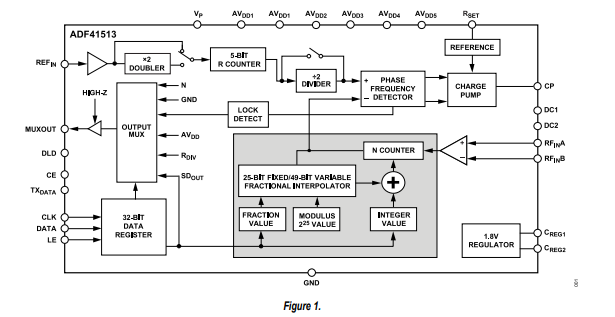

MHz(小数 N 模式),可实现更高的相位噪声和杂散性能。使用 49 位分值时,可变模数 Δ-Σ 调制器可以实现极精细的分辨率。ADF41513 可用作整数 N 锁相环 (PLL) 或小数

2025-04-25 10:04

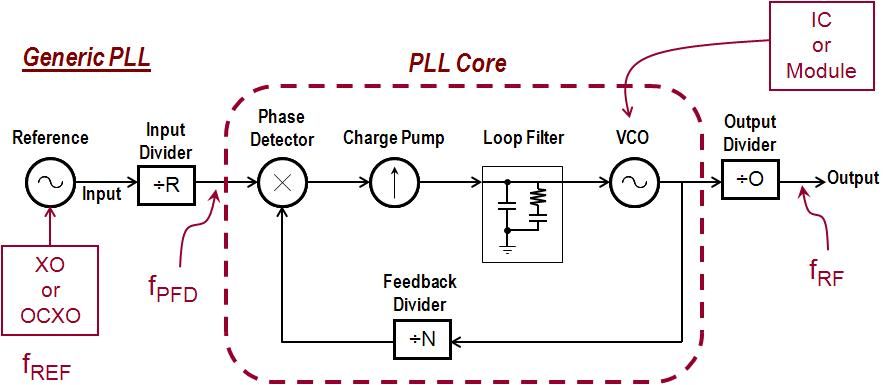

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

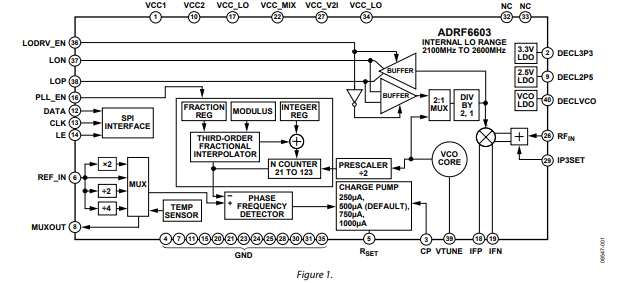

ADRF6603是一款高动态范围有源混频器,集成小数N分频锁相环(PLL)和压控振荡器(VCO),用于内部混频器LO的产生。 ADRF6603与ADRF6602共同构成了一个集成PLL/混频器系列,涵盖2100

2025-03-28 16:48

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22

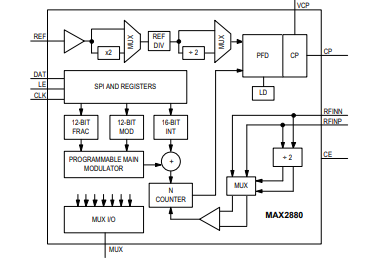

MAX2880为高性能锁相环(PLL),提供整数或分数N分频工作模式。器件配合外部参考时钟振荡器、环路滤波器和VCO,可以构成超低噪声、低杂散频率合成器,可接受高达12.4GHz的RF输入。

2025-04-25 14:21

在产生高频、高线性度信号源时,低相位噪声至关重要。相位噪声是信号相位不希望的变化或变化的量度。它是在频域中测量的,相当于时域中的抖动。使用PLL频率合成器时,总相位噪声由各种电路模块和组件的汇编

2023-01-09 16:23