作者:京微雅格产品市场经理 倘余清EMIF总线概述外部存储器总线(EMIF, External Memory Interface)

2019-05-30 05:00

最近做的东西涉及到将原有的DSP+FPGA架构的程序移植到ZYNQ-7系列FPGA上,请问如何将原DSP程序移植到ZYNQ-7的ARM上,可不可以做一个EMIF总线和AXI总线转换的模块呢?

2014-05-12 21:51

,且点 的密度高! 我们现在想EMIF-B总线想读/写13片数据锁存器(作为开关量的输入输出使用)。 需要解决的问题: 如果我使用CPU读写总线EMIF-B会与EDMA

2020-07-30 17:10

功能框图 SDRAM 和 异步存储器共用EMIF引脚说明EMA_D[x:0] EMIFA数据总线 EMA_A[x:0] EMIFA地址总线当和SDRAM存储器连接时,地址线主要用于提供SDRAM的行列

2015-11-16 15:01

过程中加入了充分长时间的延时后结果正确了。想请教各位专家,出现这种问题的原因是什么?会不会两个核同时data sorting存数且由于这种存数方式时间较长而引起了DDR3 EMIF的总线冲突呢?困扰了好一阵子,还望高手指导,不胜感激!!!

2018-06-25 07:14

我想在多处理器系统中使用 EMIF。 为此,应不时将地址和数据总线设置为高阻抗状态。 可能吗? 我找不到图纸中连接 EMIF 总线的位置? 直接连接到 PIN 或

2024-03-05 06:51

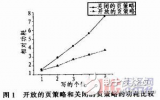

摘要:为了降低DSP外部SDRAM存储系统的功耗,针对DSP访问片外SDRAM的功耗来源特点,提出了基于总线利用率动态监测的读写归并方案。该方案动态监测外部存储器接口(EMIF)总线的利用率,根据

2017-10-30 16:34

最近在调试6455 DSP flash加载功能,一直不成功。今天用示波器抓了下上电时刻CE3片选对flash读数据波形(CE3,OE,DATA0),发现emif总线只读了大约200个字节数据就不

2020-05-26 09:17

为了降低DSP外部SDRAM存储系统的功耗,针对DSP访问片外SDRAM的功耗来源特点,提出了基于总线利用率动态监测的读写归并方案。该方案动态监测外部存储器接口(EMIF)总线的利用率,根据

2011-01-14 17:40

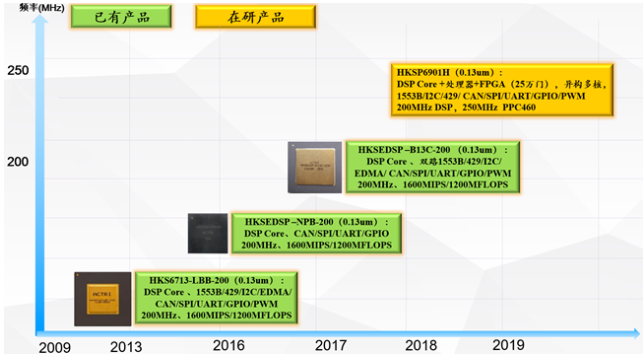

采用HKS6713-LBB-200作为核心控制处理器,实现1路1553总线控制,4路RS422接口控制和1路RS232调试接口。另外,采用EMIF总线通过板间连接器进行模块扩展。

2022-07-01 15:26