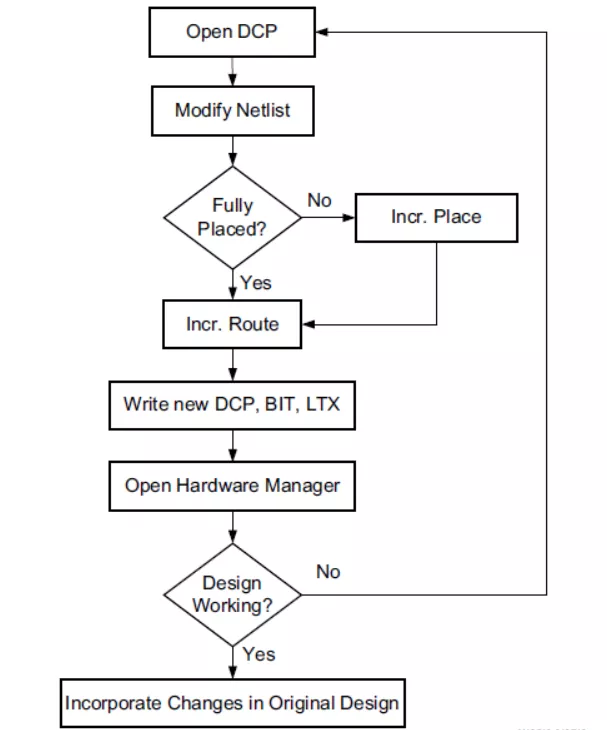

ECO 指的是 Engineering Change Order ,即工程变更指令。目的是为了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证的功能和时序。ECO 是从 IC 设计领域继承而来,Vivado上 的

2022-08-02 09:18

ECO待机开关电路电路

2011-03-31 15:09

GOF ECO不仅大大缩短了芯片ECO的Turn-around时间,还大大提升了芯片复杂逻辑ECO的成功率。

2022-11-07 14:39

大型SOC项目的综合非常耗时间,常常花费好几天。当需要做功能ECO时,代码的改动限定在某些子模块里,设计人员并不想重跑一次完整的综合,这种方法缩短了一轮ECO的时间,保证了项目进度。

2024-03-11 10:41

对网表或是布局布线进行局部编辑,从而在最短时间内,以最小的代价完成个别的设计改动需求。ECO指的是Engineering Change Order,即工程变更指令。

2017-11-18 18:26

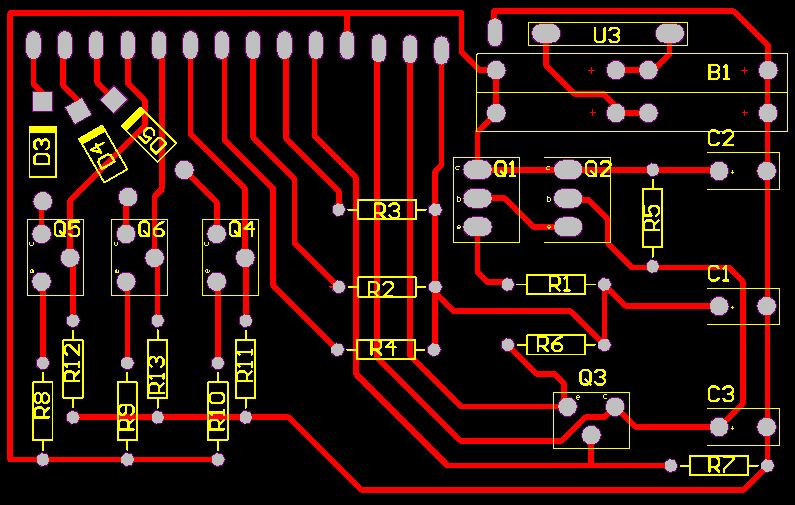

在Altium Designer中,我们可以用Altium Designer设计同步装置把设计资料从一个区域转到另一个区域,它包括比较工具、ECO以及UPDATER。它可以用于原理图和PCB之间的转换,Altium Designer中导入网络表不在是必须的。

2019-07-13 10:00

工程更改(ECO)将推高设计成本,造成产品开发大量延迟,进而延迟产品上市时间。然而,通过认真思考经常发生问题的七大关键领域,可以规避大多数ECO。

2018-05-18 15:51

在初始设计的早期阶段,DFT还没被允许之时,测试成为了一个大问题,ECO也就产生了。在一些极端情况下,如果ECO也不能解决的话,就需要重新设计才能解决问题。

2019-01-15 15:17

工程更改(ECO)将推高设计成本,造成产品开发大量延迟,进而延迟产品上市时间。

2014-08-25 14:42

PCB拼板是PCB厂经常要做的事情,进行拼板需要注意哪些事项?PCB拼板有哪些要则?

2019-05-31 09:36