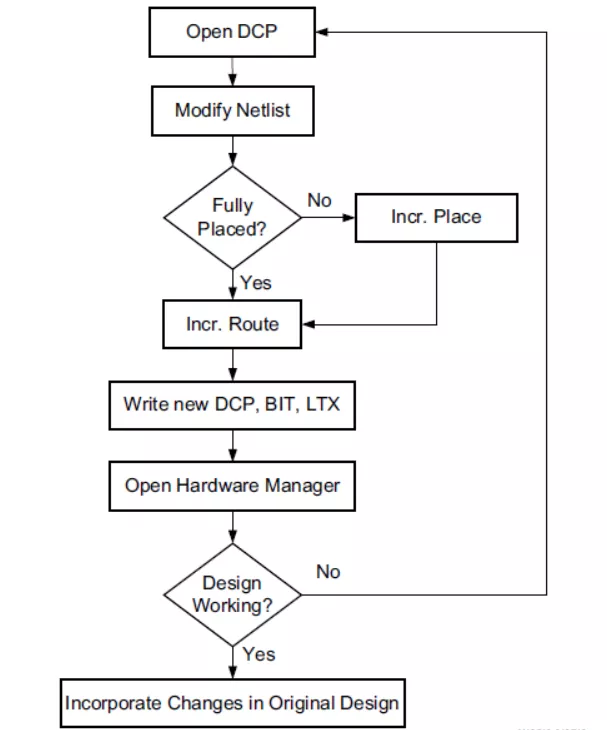

ECO 指的是 Engineering Change Order ,即工程变更指令。目的是为了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证的功能和时序。ECO 是从 IC 设计领域继承而来,Vivado上 的

2022-08-02 09:18

Spatiotemporal Multiplier Networks for Video Action Recognition 2017CVPR Christoph Feichtenhofer

2017-11-28 14:33

ECO待机开关电路电路

2011-03-31 15:09

GOF ECO不仅大大缩短了芯片ECO的Turn-around时间,还大大提升了芯片复杂逻辑ECO的成功率。

2022-11-07 14:39

大型SOC项目的综合非常耗时间,常常花费好几天。当需要做功能ECO时,代码的改动限定在某些子模块里,设计人员并不想重跑一次完整的综合,这种方法缩短了一轮ECO的时间,保证了项目进度。

2024-03-11 10:41

对网表或是布局布线进行局部编辑,从而在最短时间内,以最小的代价完成个别的设计改动需求。ECO指的是Engineering Change Order,即工程变更指令。

2017-11-18 18:26

如下图所示,有时候,这个毛刺信号比较小,可以忽略;但是,当毛刺信号足够高而且持续时间较长,这就有可能导致逻辑功能发生变化,破坏了门电路所保存的状态,使得电路发生故障。因此,在最后timing signoff中,noise引起的glitch是我们必须要修复的violation。

2019-01-14 13:55

大多数芯片设计团队在这一环节使用新思科技的数字设计产品系列,即Design Compiler或Fusion Compiler解决方案。

2022-10-19 10:05

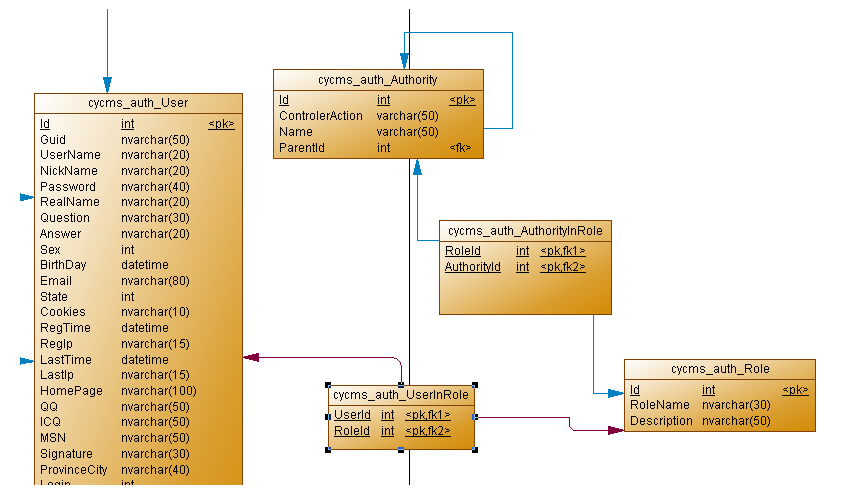

标识 权限 因为后台的访问控制都是基于Action级别 的控制,而我们使用系统都是以功能模块为最小单位的控制,所以我们首先需要建立一个Action和功能块的对应关系,如:创建用户功能

2020-11-06 11:23