我们知道,不论是哪一级的验证,最终都是通过 pin 连接到 DUT 上向其施加激励,**对于 UVM 验证平台中,使用虚接口来实现 DUT 和验证平台的通信

2023-03-21 11:20

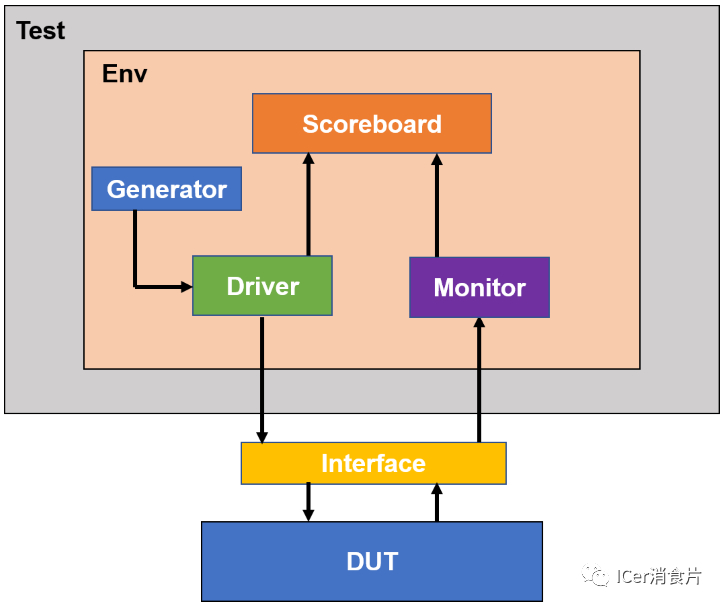

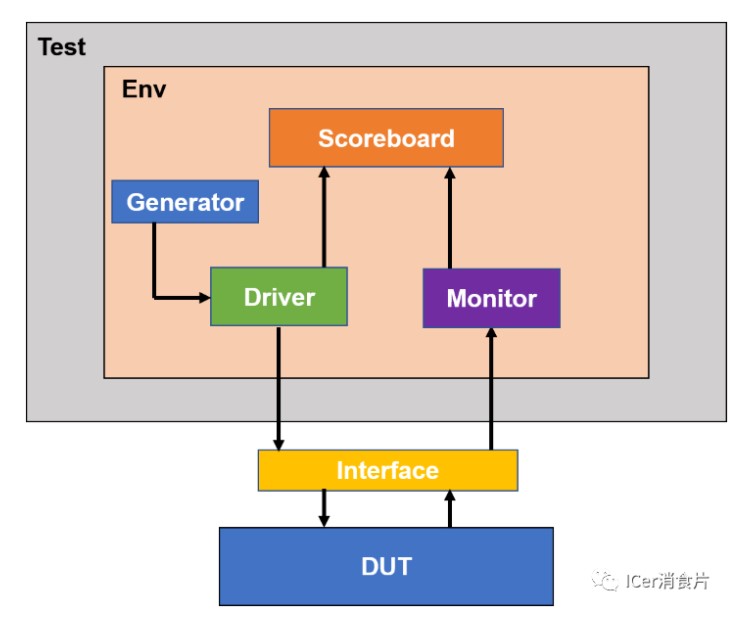

TestBench即测试平台,是为了检验待测设计(design under test,DUT)而搭建的验证环境。

2023-06-12 17:38

TestBench即测试平台,是为了检验待测设计(design under test,DUT)而搭建的验证环境。

2023-02-24 17:19

在UVM寄存器模型的操作中,寄存器用于设置DUT状态和芯片状态信息的上报,有前门和后门读写两种方式。

2023-08-19 09:50

定义一个配置对象:首先,需要定义一个包含DUT配置的UVM配置对象。这个对象通常会包含被测设备的所有可配置参数。

2023-06-06 12:55

寄存器模型保持着DUT内部寄存器值的 镜像(mirror) 。 镜像值不能保证是正确的,因为寄存器模型只能感知到对这些寄存器的外部读写操作。 如果DUT内部修改了寄存器中的字段,镜像值就会 过时

2023-06-24 12:02

编写一个创建模块dut实例(具有任何实例名称)的测试平台,并创建一个时钟信号来驱动模块的clk输入。时钟周期为 10 ps。时钟应初始化为零,其第一个转换为 0 到 1。

2023-03-13 09:19

用网络分析仪测试DUT的两个通道,发现驻波比差很多,第一反应是两个通道的阻抗一致性是不是没做好,打开阻抗测试界面,结果显示两个通道的阻抗差不多,而且满足阻抗要求…… 肯定是哪里操作有问题!来~~重新

2021-03-24 09:53

DUT07高频开关电源系统是以DZW75-48/50(50II)型整流器模块为基础,配以JP50-50II)型交流配电箱。如图所示为P50-交流配电箱原理图。

2011-06-21 10:13

在QCC517x的earbud工程中,已经能够支持用SPP进行DUT测试了(当然headset工程其实也已经支持了,前提是需要打开一些设置,这个不是本文的范畴,这里暂不做详细说明

2023-06-05 09:06