在DRC的修复过程中,我们可以先分析并修复PR工具里面的DRC,等DRC的数目比较少了之后,我们就可以把PV工具里面signoff DRC的结果load到PR工具里面去

2023-11-02 10:57

DRC的全称为design rule check,也就是设计规则检查。广义上DRC会包含很多分类,只要是设计规则广义上都可以成为DRC。

2023-12-04 13:55

某些DRC在Innovus里面检查可能没有问题,但是到了Calibre/ICV检查可能发现有DRC问题。

2023-11-16 11:05

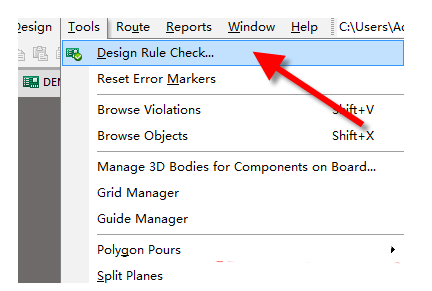

Altium有时候总是显示DRC错误,不知道哪里出了问题,下面小编带大家学习一下常见的DRC检查有哪些?

2018-09-23 12:27

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23

前期为了满足各项设计的要求,我们会设置很多约束规则,当一个PCB单板设计完成之后,通常要进行DRC检查。那么DRC检查到底有哪些具体事项?

2019-05-29 14:43

Create Report File 执行完DRC之后,Altium会创建一个关于规则检查的报告,对报错信息会给出详细的描述并会给出报错的位置信息,方便我们设计者对报错信息进行解读。

2020-10-06 17:49

由于传统DRC是计算RMS,必然有几个周期的波形是可能失真的。ACM8687除了RMS DRC之外,采用专利技术,加入PEAK检测。

2024-04-26 17:31

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado

2022-08-02 10:10

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整

2024-10-24 15:08