(能量平衡、停留时间分布、热-应力结果),帮助用户分析材料在挤出机中的变化规律。同时,软件特有的DoE实验设计功能,可快速筛选可行工艺,降低研发成本。

2025-02-08 16:31

实验设计(DOE)是半导体工程研发中一个强大的概念,它是研究实验变量敏感性及其对器件性能影响的利器。如果DOE经过精心设计,工程师就可以使用有限的

2023-04-13 14:19

虚拟DOE能够降低硅晶圆测试成本,并成功降低DED钨填充工艺中的空隙体积

2023-07-10 10:18

电磁脉冲辐照效应实验方法 电磁脉冲对电予系统的辐照效应实验方法,简单地说就是将被测电子系统置于电磁脉冲辐射场中,接受电磁脉冲的照射,研究被测系统在电磁脉冲照射下受干扰、损伤的情况。 实验配置如图1

2017-11-30 08:28

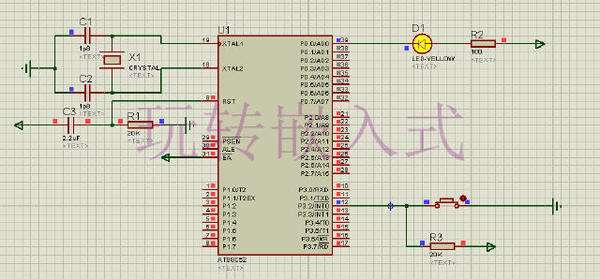

实验结果:当杜邦线另一端接电源时,led灭;当接地时,led就亮 结论:无论配置与否,51单片机的外部中断这个外设都在工作着,不可能禁止

2018-11-23 15:16

针对目前嵌入式教学实验平台资源的不足,为了使理论与实践相结合、软硬件联系更紧密,设计提出了一套Cortex—A8内核的嵌入式系统实验平台方案,采用主流硬件构成,阐述了各实验设计流程,最后给出了嵌入式

2018-08-05 10:49

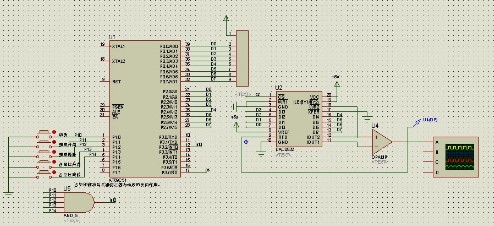

这个proteus仿真是一个网友做的,该仿真可以生成方波、正弦波、锯齿波和三角波,并且还可以用按键调整波形。 不过,对初学者来讲,可能有点复杂。对于本科生来说,这个仿真几乎可以作为毕业论文了吧。当然,需要用实际元器件来调试,制作pcb,焊接。 我做的生成锯齿波和生成正弦波的仿真,可以作为学习这个仿真的阶梯。 这个仿真主要是用到溢出中断,和外部键盘中断。熟悉中断,和定时器的编程后,实现这个仿真其实也很简单。

2018-12-28 15:50

负载效应 (loading) 的控制对良率和器件性能有重大影响,并且它会随着 FinFET(鳍式场效应晶体管)器件工艺的持续微缩变得越来越重要[1-2]。当晶圆的局部刻蚀速率取决于现有特征尺寸和局部图形密度时,就会发生负载效应。刻蚀工艺 loading 带来的器件结构上的微小变化可能会对器件良率和性能产生负面影响,例如在伪栅多晶硅刻蚀过程中,由于刻蚀的负载效应,可能会在栅极和鳍结构交叉区域产生多晶硅边角残留,进而造成 FinFET 结构的改变,并直接影响 FinFET 栅极的长度和电学性能。多晶硅边角残留对良率和器件性能的影响,包括可接受的残留的尺寸大小,可使用 SEMulator3D 提前预测。

2023-01-06 10:48

程序一:在液晶屏上显示一个1 //在液晶屏上显示一个字符 #include #define uchar unsigned char #define uint unsigned int //端口设置 sbit lcden=P3^4; sbit lcdrs=P3^5; //延迟函数,大约1秒

2018-11-08 16:37

首先来看看所需要的清单:51单片机STC12C5A60S2、12864液晶屏、温度传感器DS18B20、时钟芯片DS1302、光敏电阻、四腿按键等。

2018-11-10 11:37