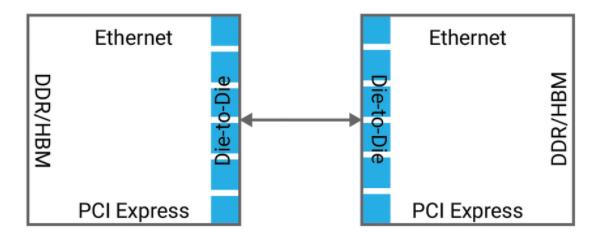

本文介绍了 die-to-die 连接的几种不同用例,以及在寻找用于 die-to-die 连接的高速 PHY IP 也可以使用基于有机基材的传统低成本封装。

2020-05-18 09:57

小芯片(Chiplet)已经成为当今大厂角逐的一大方向,对于小芯片来说,需要一种芯片到芯片的互连/接口技术,现在已有多种Die-to-Die接口可以满足这类需求。其中,基于SerDes的或并行

2022-02-15 15:14

小芯片(Chiplet)已经成为当今大厂角逐的一大方向,对于小芯片来说,需要一种芯片到芯片的互连/接口技术,现在已有多种Die-to-Die接口可以满足这类需求。其中,基于SerDes的或并行

2022-02-23 16:32

在半导体行业中,“die”,“device”,和“chip”这三个术语都可以用来指代芯片。

2024-02-23 18:26

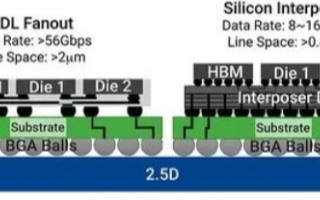

XSR 即 Extra Short Reach,是一种专为Die to Die之间的超短距离互连而设计的芯片间互连技术。可以通过芯粒互连(NoC)或者中介层(interposer)上的互连来连接多个芯片,在多芯片计算体系结构的设计中起到了重要的作用。

2025-06-06 09:53

Wafer、die、chip是半导体领域常见的术语,但是为什么单颗裸芯会被称为die呢?

2024-01-24 09:14

通用芯粒互连技术(UCIe)为半导体行业带来了诸多可能性,在Multi-Die设计中实现了高带宽、低功耗和低延迟的Die-to-Die连接。它支持定制HBM(cHBM)等创新应用,满足了I/O裸片

2025-08-04 15:17

Multi-Die系统的基础构建,亦是如此,全部都需要细致入微的架构规划。 对于复杂的Multi-Die系统而言,从最初就将架构设计得尽可能正确尤为关键。 Multi-Die系统的出现,是为了应对设计规模增加和系统复

2023-09-22 11:07

随着移动通信技术的发展,系统越趋复杂,同时产品集成度要求也越来越高,系统级封装(SiP)成为了最具潜力的候选方案之一,其将不同制程工艺节点的裸芯片Die集成在一个封装里,在满足器件高性能需求的同时,也减少了芯片设计公司的研发成本和时间。

2023-07-17 16:38

可能你偶尔会听见硬件工程师,或者芯片设计工程师讲述一些专业名词,比如今天说的wafer、die、cell等。

2023-12-27 13:45