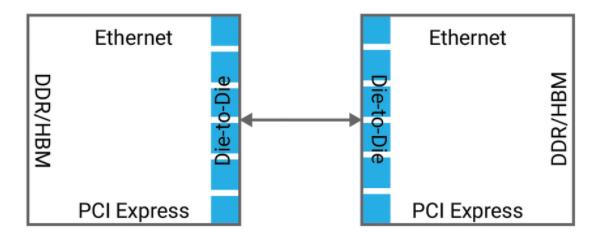

本文介绍了 die-to-die 连接的几种不同用例,以及在寻找用于 die-to-die 连接的高速 PHY IP 也可以使用基于有机基材的传统低成本封装。

2020-05-18 09:57

量产测试的速度和覆盖范围。而且这些方法已经标准化,企业可以在最终产品制造的不同阶段(从晶圆测试到芯片测试再到板级测试)使用通用的测试指标和接口,以提高效率。本文介绍了如何使用Die-to-Die

2020-10-25 15:34

电子发烧友网为你提供TI(TI)TLC555-DIE相关产品参数、数据手册,更有TLC555-DIE的引脚图、接线图、封装手册、中文资料、英文资料,TLC555-DIE真值表,TLC555-

2019-04-18 20:08

芯砺智能近日宣布,其全自研的Chiplet Die-to-Die互连IP(CL-Link)芯片一次性流片成功并顺利点亮。这一重大突破标志着芯砺智能在异构集成芯片领域取得了领先地位,为人工智能时代的算力基础设施建设提供了更加多元灵活的互连解决方案。

2024-01-18 16:03

简介 半导体行业面临的一个主要挑战是无法在量产阶段早期发现产品缺陷。如果将有缺陷的产品投放市场,将会给企业带来巨大的经济和声誉损失。对超大规模数据中心、网络和 AI 应用的高性能计算片上系统 (SoC) 的设计开发者而言,尤其如此,因为任何产品缺陷都可能对 AI 研发的工作量或数据处理产生灾难性影响。 半导体行业已经开发出了一系列测试方法,来提高量产测试的速度和覆盖范围。而且这些方法已经标准化,企业可以在最终产品制造的不

2020-10-30 18:25

流媒体、监视和监控数据、联网传感器、社交媒体、在线协作、远程学习、增强和虚拟现实、在线游戏……随着无穷无尽的在线应用不断涌现,在线数据量出现激增。预计在未来 10 年中,数据流量的年增长率将超过 400 倍(图 1)。这种数据流量的快速增长,将对数据接口 IP 提出更高要求,需要其在速度和延迟方面,尤其是云基础架构中都有显著改善。本文将解释在数据中心内、数据中心之间、服务器内以及 SoC 内等,加速数据传输和管理的技术发展。

2022-04-11 18:13

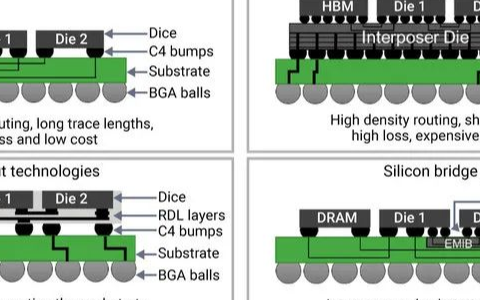

随着带宽需求飙升至新高度,多芯粒系统正成为许多应用领域的解决方案。通过在单一封装中异构集成多个芯粒,Chiplet芯粒系统能够为人工智能、高性能计算和超大规模数据中心提供更高的处理能力和性能。一系列技术创新为多芯粒系统的出现铺平了道路,其中关键的一项创新是UCIe标准。UCIe标准于2022年3月推出,是芯粒互联国际标准,UCIe有助于构建一个更广泛的、经过验证的芯粒生态系统。

2024-12-10 11:33

当AI大模型参数规模突破万亿级别,传统单芯片设计遭遇物理极限。芯粒技术通过模块化组合突破瓶颈,而芯片间互联带宽成为决定性因素之一。近期,UCIe 3.0规范将数据传输速率从UCIe 2.0的32 GT/s提升至48 GT/s和64 GT/s两档,实现带宽密度翻倍增长。

2025-08-18 16:50

新思科技IP营销和战略高级副总裁John Koeter表示:裸片拆分和分解的趋势下,需要超短和特短距离链接,以实现裸晶芯片之间的高数据速率连接。

2021-06-15 12:05

Multi-Die设计是一种在单个封装中集成多个异构或同构裸片的方法,虽然这种方法日益流行,有助于解决与芯片制造和良率相关的问题,但也带来了一系列亟待攻克的复杂性和变数。尤其是,开发者必须努力确保

2025-02-25 14:52