最近在做设计的时候,发现之前对DFF的理解有些模糊,直到有次在实践中遇到了一些问题,含糊其词的也不能解决问题,于是乎就把DFF理解透彻透彻,毕竟这可是时序电路的基本概念。

2022-07-12 10:22

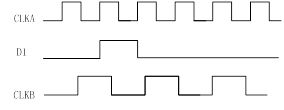

对于DFF,之前理解的,DFF在时钟的上升沿进行对D端的数据采集,再下一个时钟的上升沿来临,Q端输出D端采集的数据。

2023-05-10 09:02

中国科学院国家空间科学中心太阳活动与空间天气重点实验室陈睿副研究员、韩建伟研究员团队以130nmSOI工艺制备的DFF时序逻辑电路为对象,初步研究揭示了SESD导致星用DFF电路故障的特征规律

2022-09-06 14:47

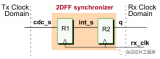

用敲两级DFF的办法(两级DFF同步器)可以实现单比特信号跨时钟域处理。但你或许会有疑问,是所有的单比特信号跨时钟域都可以这么处理吗?

2023-06-28 11:39

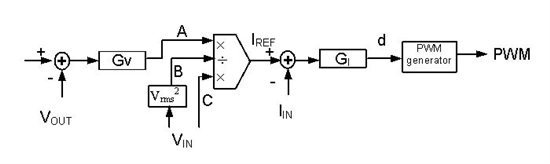

作者:Bosheng Sun 几十年来,平均电流模式控制一直用于功率因数校正 (PFC),而且在商业市场也有各种采用这种控制算法的 PFC 控制芯片。 图 1 是这种平均电流模式控制的形象介绍

2021-11-10 09:43

几十年来,平均电流模式控制一直用于功率因数校正 (PFC),而且在商业市场也有各种采用这种控制算法的 PFC 控制芯片。 图 1 是这种平均电流模式控制的形象介绍。图 1 . PFC 的平均电流模式

2017-04-18 14:39

最经典的2DFF 1-bit同步器如下,下图结构通常用于单bit控制信号的异步处理

2024-01-18 09:24

Scan stitching 是把上一步中得到的Scan DFF的Q和SI连接在一起形成scan chain。在芯片的顶层有全局的SE信号,以及scan chain的输入输出信号:SI 和 SO。通过scan chain的连续动作,就可以把问题从对复杂时序电路的测

2023-10-09 16:53

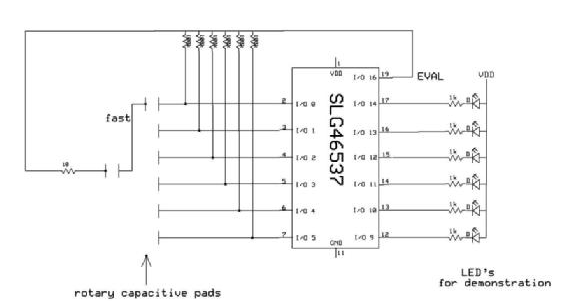

DFF锁存器保持ASM结果稳定,以便在ASM复位期间不会切换最终输出。驱动开漏NMOS输出引脚所需的极性,要求我们配置具有反相输出的DFF。

2019-02-18 15:39

我们在网表里直接插入了RTL的always语句,对wr_data_7_进行了打拍和简单逻辑处理(新加的逻辑所需要的输入信号都可以在原网表中找到),把处理后的信号wr_data_7_new_d接到原DFF的D端,如下图中的箭头。这种在网表里直接插入和修改的RTL也叫做RTL补丁。

2023-06-06 16:20