DDS(Direct Digital Synthesizer,直接数字频率合成器)技术是一种频率合成方法,其输出频率与时

2024-10-06 15:27

作为fpga小白,在做fpga控制dds输出频率和幅度的设计,在大神指导下完成了mif文件的生成,但是生成的是10个mif文件,同学告诉我应该下一步在fpga中写一个片选,想问问应该怎么写?写在哪?

2019-02-20 23:59

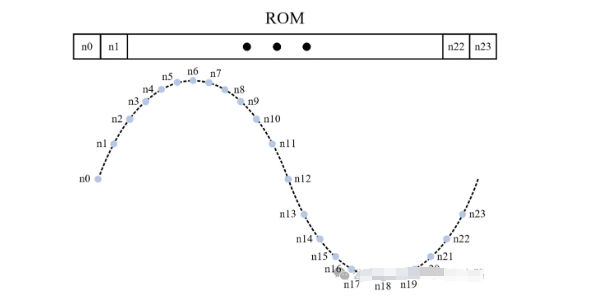

现代直接数字频率合成器(DDS)通常利用累加器和数字频率调谐字(FTW)在累加器输出端产生周期性的N位数字斜坡(见图1)。 此数字斜坡可依据公式1定义

2017-11-10 15:49

现代直接数字频率合成器(DDS)通常利用累加器和数字频率调谐字(FTW)在累加器输出端产生周期性的N位数字斜坡(见图1)。此数字斜坡可依据公式1定义

2017-09-12 18:59

用于大步进频率合成技术中。DDS(直接数字合成)是近年来迅速发展起来的一种新的频率合成方法。这种方法简单可靠、控制方便,且具有很高的频率分辨率和转换速度,缺点是

2011-07-16 09:09

关? 3.AD5934是否能达到1k-100kHz频率输出范围?我注意到设置起始频率100kHz,起始频率寄存器还没有到0xFFFFFF。那么如果我设置起始

2023-12-01 06:55

直观的说明。虽然不是一一对应的比较,但它显示了我要谈到的内容——相比于PLL,DDS的输出频率中有更多(且更大)的频率杂散。可以采取一些措施来解决这个问题。基于PLL的

2019-02-13 11:54

最近在使用dds芯片时遇到一个问题,理论上dds输出信号的最小分辨率是fs/2N,即时钟频率/相位累加器大小,通过改变控制字M的大小就可以得到想要的

2018-08-03 07:56

杂散抑制差和输出频率低是DDS的两大缺点,并且随着输出带宽的增加杂散性能更加恶化。传统的解决方法是采用更好的算法和改进DDS

2009-03-11 22:09

大家谁用过DDS(AD9850模块,买的现成的),测试程序是1K的,这没错,可是改成别的频率,它就不对了,求大神一个调好的程序,谢谢

2013-08-09 12:31