DDR6 RAM 是 目前DDR 迭代中的最新版本,最大的数据速率峰值超过 12000 MT/s。

2024-12-03 16:47

DDR6和DDR5内存的区别有多大?怎么选择更好? DDR6和DDR5是两种不同的内存技术,它们各自在性能、功耗、带宽等方面都有不同的特点。下面将详细比较这两种内存技术

2024-01-12 16:43

当下,DDR5内存还远未到要主流普及的程度。不过,DRAM内存芯片的头部厂商们已经着手DDR6研制了。

2022-07-25 11:25

电子发烧友网综合报道,据业界消息,三星电子、SK海力士、美光均已完成DDR6规格的初期原型开发,正与英特尔、AMD、英伟达等CPU/GPU厂商共同推进平台验证。当前目标性能为8800MT/s,后续

2025-07-31 08:32

据外媒消息,第二大DRAM芯片厂商SK海力士已着手第六代DDR内存即DDR6的研发,预期速率12Gb/s,也就是DDR6-12000。

2019-01-30 15:06

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23

但在 MSAP 中,除了电路之外的区域都经过涂层处理,而空白区域则进行了电镀,从而可以实现更精细的电路。三星副总裁说,随着存储芯片容量和数据处理速度的增加,封装的设计必须适应这一点。Ko说,随着层数的增加和工艺变得更加复杂,内存封装市场也有望成倍增长。

2022-07-25 15:59

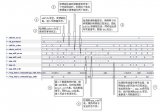

DDR SDRAM的接口特性:其输入输出引脚与SSTL-Ⅱ电气特性兼容,内部提供了DDR触发器、锁相环等硬件资源。使用这些特性,可以比较容易地设计性能可靠的高速DDR RAM控制器。本文介绍一种采用

2017-11-24 16:00

在 FPGA 中测试 DDR 带宽时,带宽无法跑满是常见问题。下面我将从架构、时序、访问模式、工具限制等多个维度,系统梳理导致 DDR 带宽跑不满的常见原因及分析方法。

2025-10-15 10:17

本文详细介绍了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速实时数字信号处理中大容量采样数据通过

2017-11-17 14:26