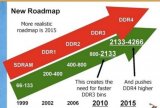

本文介绍了DDR4技术的特点,并简单介绍了ANSYS工具用来仿真DDR4的过程。文章中主要介绍的对象为DDR4 3200MHz内存,因为硬件极客对DDR4性能的不断深挖

2018-10-14 10:37

DDR5标准JESD79-5文件中没有明确的控制阻抗建议,DDR4时代基本内存条上时钟阻抗还是跟着芯片、主板走的70-80欧姆。线宽相对而言比较细。不知道你开始使用DDR

2024-07-16 17:47

DDR5已经开始商用,但是有的产品还才开始使用DDR4。本文分享一些DDR4的测试内容。DDR4 和前代的 DDR3 相

2024-01-08 09:18

VTT上拉电阻放置在相应网络的末端,即靠近最后一个DDR4颗粒的位置放置;注意VTT上拉电阻到DDR4颗粒的走线越短越好,走

2019-04-16 09:51

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走

2018-03-08 17:18

DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走

2018-06-16 07:17

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线

2019-10-04 17:17

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚

2020-11-22 11:54

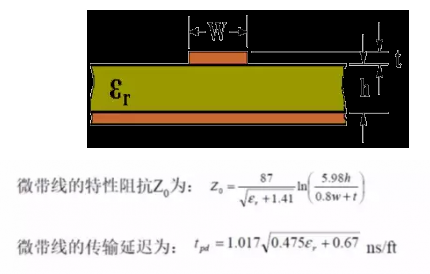

多长的走线才是传输线? 这和信号的传播速度有关,在FR4板材上铜线条中信号速度为6in/ns。简单的说,只要信号在走线上

2020-11-06 10:25

采用法拉第电笼进行保护。今天我来说说防止电磁干扰的PCB走线和板层设计。 说到走线和板层,我们就会想到2层板

2020-09-14 09:51