本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB

2014-07-24 11:11

我们通过Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封装,速度等级等信息。

2019-03-03 11:04

线短而粗,回路尽量短;CPU和颗粒周边均匀摆放一些储能电容,DDR3颗粒每片至少有一个储能电容。

2021-04-09 09:56

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通

2017-11-18 18:51

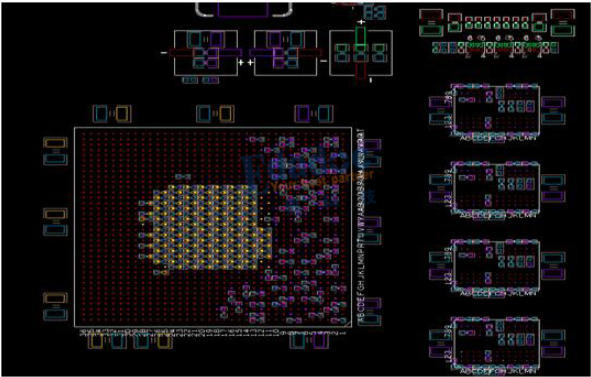

DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度、紧凑型的电路板设计。

2018-06-16 07:17

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用

2022-08-16 10:28

本文以Kintex-7系列XC7K410T FPGA芯片和两片MT41J128M16 DDR3 SDRAM芯片为硬件平台,设计并实现了基于FPGA的视频图形显示系统的DDR3多端口存储管理。##每片

2015-04-07 15:52

从那时起,采用DDR2、甚至最新的DDR3 SDRAM的新设计让DDR SDRAM技术黯然失色。DDR内存主要以IC或模块的形式出现。如今,

2011-07-11 11:17

为了满足高速图像数据采集系统中对高带宽和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的设计方法,提出了一种基于Verilog-HDL 语言的DDR3 SDRAM

2017-11-17 14:14

突发长度,由于DDR3的预期为8bit,所以突发传输周期(BL,Burst Length)也固定位8,而对于DDR2和早期的DDR架构的系统,BL=4也是常用的,DDR3

2018-06-21 09:20