本文以一个案例的形式来介绍lattice DDR3 IP核的生成及调用过程,同时介绍各个接口信号的功能作用

2022-03-16 14:14

1. 背景 这篇文章主要介绍了DDR3IP核的写实现。 2. 写命令和数据总线介绍 DDR3 SDRAM控制器IP

2020-12-31 11:17

讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Artix-35T

2021-01-01 10:09

本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载

2023-09-01 16:20

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23

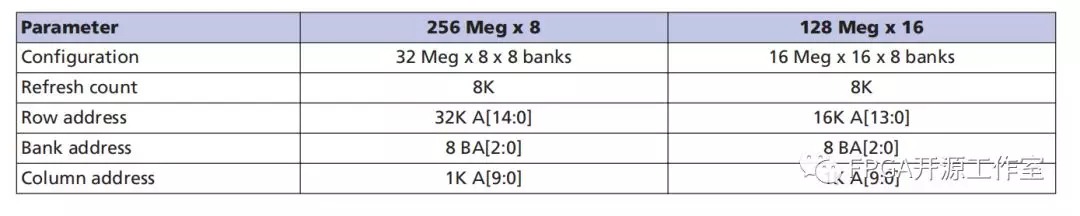

我们通过Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封装,速度等级等信息。

2019-03-03 11:04

学完SDRAM控制器后,可以感受到SDRAM的控制器的书写是十分麻烦的,因此在xilinx一些FPGA芯片内已经集成了相应的IP核来控制这些SDRAM,所以熟悉此类IP核

2019-11-10 10:28

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG

2022-08-16 10:28

DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP

2020-11-26 15:02

为解决超高速采集系统中的数据缓存问题,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核进行了DDR3

2017-11-16 14:36