Cadence 16.6 12层板高速PCB设计DDR3实例 视频教程

2014-09-23 01:20

如何设计4层PCB板叠层?

2019-07-31 10:49

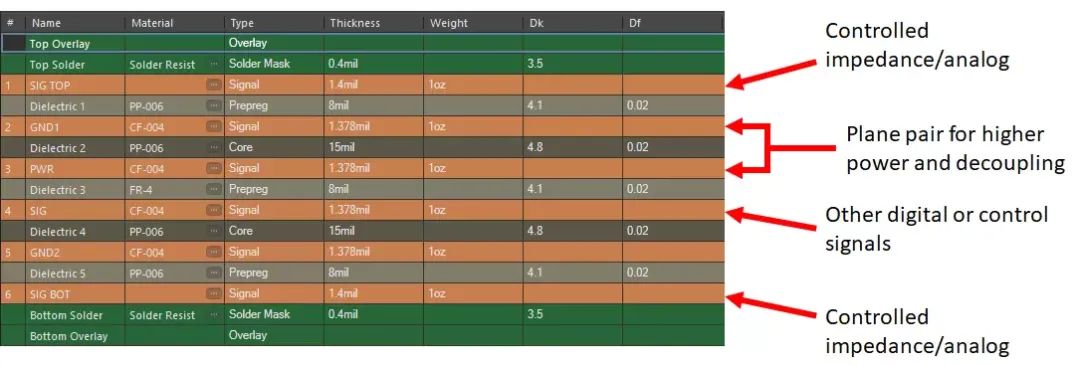

4层PCB上的空间用完后,就该升级到6层电路板了。额外的层可以为更多的信号、额外的平面对或导体的混合提供空间。如何使用这些额外的

2023-10-16 15:24

8层通孔板1.6mm厚度叠层与阻抗设计 在8层通孔板叠

2023-08-21 17:16

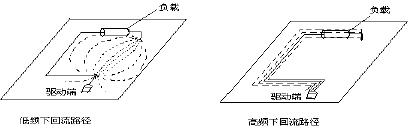

的堆叠在变得尤为重要。 良好的PCB叠层设计对于减少PCB回路和相关电路的辐射至关重要。相反,不良的堆积可能会显着增加辐射,从安全角度来看这是有害的。 什么是

2020-11-03 10:33

3层是信号走线层,但对应的第4层却是大面积敷铜的电源层,这在PCB工艺制

2016-05-17 22:04

在8层通孔板叠层设计中,顶层信号 L1 的参考平面为 L2,底层信号 L8 的参考平面为 L7。 建议层叠为TOP-Gnd-Signal-Power-Gnd-Signa

2023-12-25 13:46

在8层通孔板叠层设计中,顶层信号 L1 的参考平面为 L2,底层信号 L8 的参考平面为 L7。 建议层叠为TOP-Gnd-Signal-Power-Gnd-Signa

2023-12-25 13:48

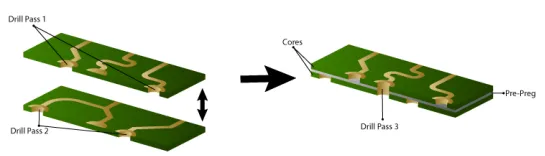

在设计2层PCB时,实际上不需要考虑PCB在工厂的结构问题。但是,当电路板上的层数为四

2023-07-19 16:19

高速PCB设计的叠层问题

2009-05-16 20:06