本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB

2014-07-24 11:11

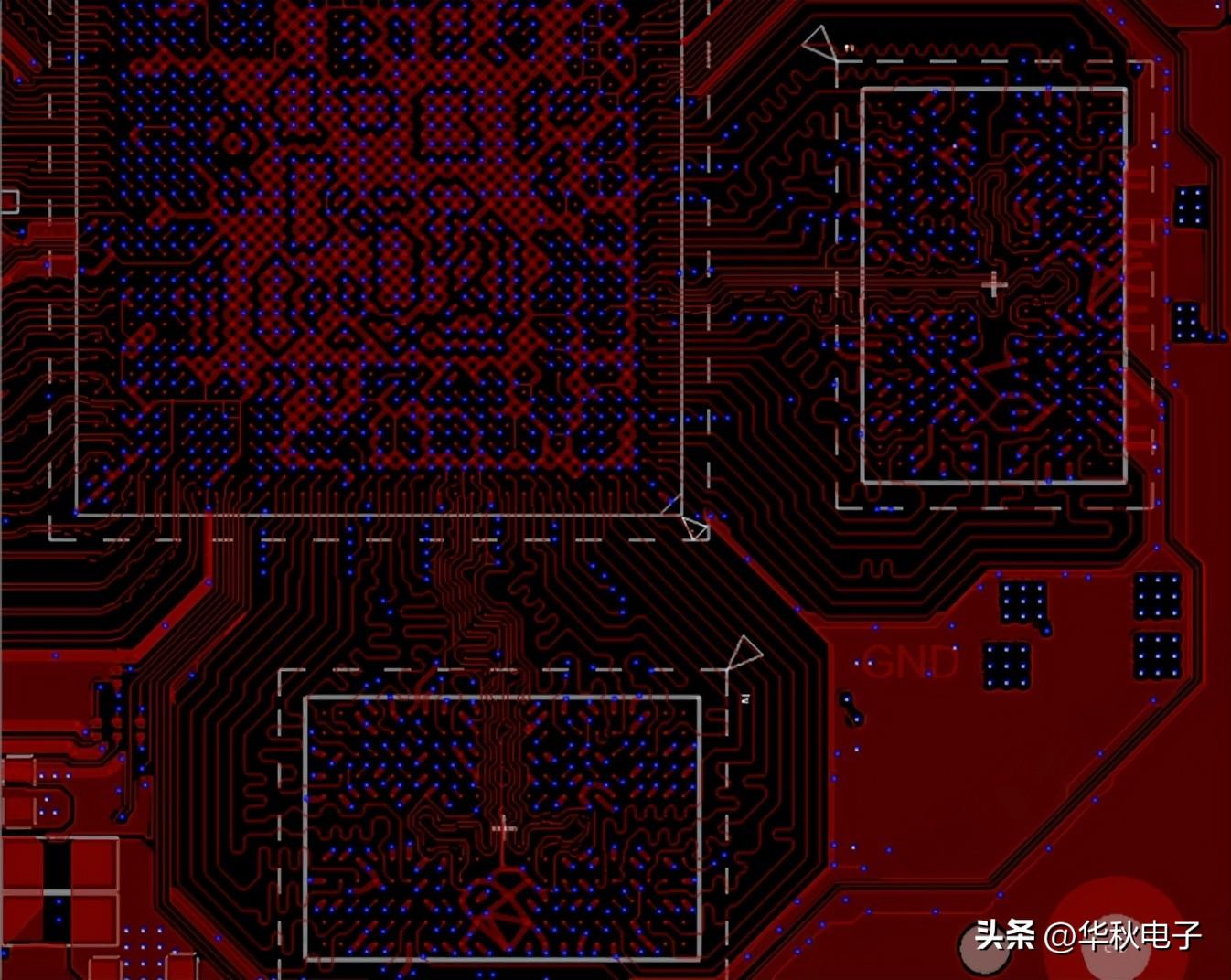

RK3588 DDR接口速率最高达4266Mbps,PCB设计难度大,所以强烈建议使用瑞芯微原厂提供的DDR模板和对应的DDR固件,

2023-08-24 08:40

RK3588 DDR接口速率最高达4266Mbps,PCB设计难度大,所以强烈建议使用瑞芯微原厂提供的DDR模板和对应的DDR固件,

2023-08-21 17:16

在高速PCB设计中,DDR模块是绝对绕不过去的一关。无论你用的是DDR、DDR2还是DDR3,只要设计不规范,后果就是—

2025-04-29 13:51

前言 上文中,我们介绍了DDR芯片的物理层及协议测试,本文我们继续给大家揭秘如何利用是德科技的ADS仿真软件辅助进行DDR的电路仿真,验证和分析。 是德科技ADS简介

2021-05-17 09:28

由于FPGA芯片是有关于DDR的设计指导文档,我司的PCB工程师和客户在投板前也反复确认了该DDR模块的设计是完全按照文档上面每一条细致的指导去布线的。

2021-03-17 15:00

PCB的DDR4布线指南和PCB的架构改进

2023-12-07 15:15

DDR3内存与DDR2内存相似包含控制器和存储器2个部分,都采用源同步时序,即选通信号(时钟)不是独立的时钟源发送,而是由驱动芯片发送。它比DR2有更高的数据传输率,最高可达1866Mbps;DDR3还采用8位预取技

2019-06-25 15:49

由于RK3588 DDR接口速率最高达4266Mbps,PCB设计难度大,所以强烈建议使用瑞芯微原厂提供的DDR模板和对应的DDR固件,

2023-08-18 10:55