本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB

2014-07-24 11:11

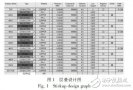

。Freescale公司P5020为处理器进行分析,模块配置内存总线数据传输率为1333MT/s,仿真频率为666MHz. 3.1仿真前准备 在分析前需根据DDR3的阻抗与印制板厂商沟通确认其

2014-12-15 14:17

研究了MPC8379E处理器的相关资料和DDR2的特性,以及它们之间PCB布线的规则和仿真设计。由于MPC8379E和DDR2都具有相当高的工作频率,所以他们之间的走线

2013-03-12 15:22

DDR2设计和仿真技术详解。

2022-10-24 15:10

通过Cadence软件建立DDRⅡ信号拓扑结构、仿真信号的串扰、码间干扰、过冲等与信号质量相关的参数,从仿真波形中可以测量出与信号时序相关的参数,从而计算出信号的时序裕量,并为

2012-02-13 15:16

RK3588 DDR接口速率最高达4266Mbps,PCB设计难度大,所以强烈建议使用瑞芯微原厂提供的DDR模板和对应的DDR固件,

2023-08-24 08:40

RK3588 DDR接口速率最高达4266Mbps,PCB设计难度大,所以强烈建议使用瑞芯微原厂提供的DDR模板和对应的DDR固件,

2023-08-21 17:16

在高速PCB设计中,DDR模块是绝对绕不过去的一关。无论你用的是DDR、DDR2还是DDR3,只要设计不规范,后果就是—

2025-04-29 13:51

前言 上文中,我们介绍了DDR芯片的物理层及协议测试,本文我们继续给大家揭秘如何利用是德科技的ADS仿真软件辅助进行DDR的电路仿真,验证和分析。 是德科技ADS简介

2021-05-17 09:28