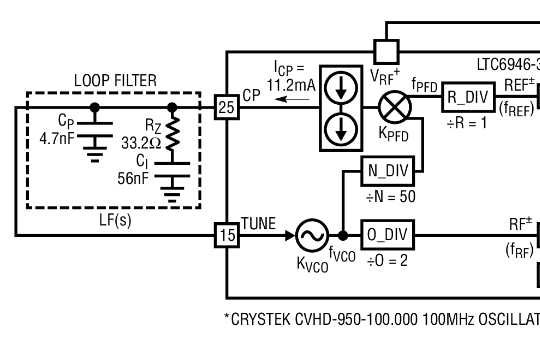

ADI最新一代高速DAC具有出色的相位噪声,可在下一代低相位噪声、快速跳频捷变RF/微波频率合成器中实现尺寸、重量、功耗/性能和成本优势。一个挑战是,为了实现这种DAC功能,固定DAC

2022-12-15 15:20

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。

2012-04-01 10:19

对于许多 DAC 应用而言,为了在不损害所关注频段之信噪比 (SNR) 的情况下实现某个频段中可用通道数目的最大化,相位噪声、噪声频谱密度 (NSD) 和无杂散动态范围 (SFDR) 指标是至关紧要的。高速 DAC 需要一个干净的

2019-10-16 17:31

接收机ADC对接收到的连续波形进行采样,发射机的DAC与接收机的ADC不可能具有完全相同的时钟频率和相位。时域的采样偏差导致频域上子载波不再正交,对于OFDM来说这是致

2017-02-11 14:16

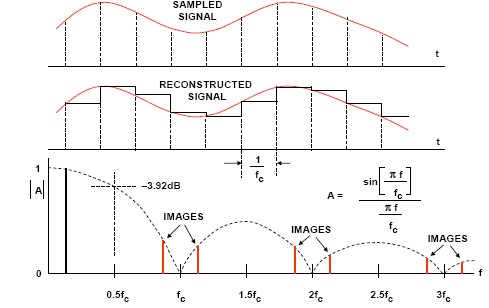

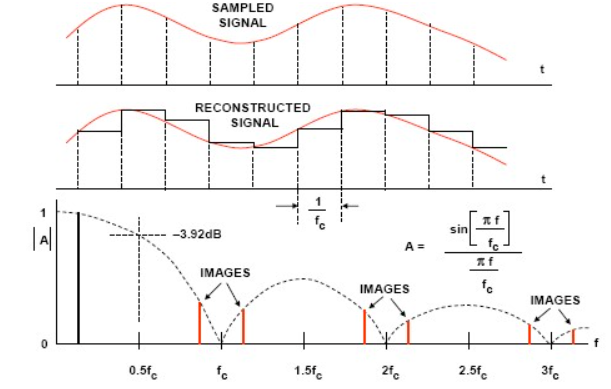

过采样和数字滤波有助于降低对ADC前置的抗混叠滤波器的要求。重构DAC可以通过类似的方式运用过采样和插值原理。

2022-08-01 09:53

在使用高速模数转换器 (ADC) 进行设计时,需要考虑很多因素,其中 ADC 采样时钟的影响对于满足特定设计要求至关重要。关于 ADC 采样时钟,有几个指标需要了解

2024-11-13 09:49

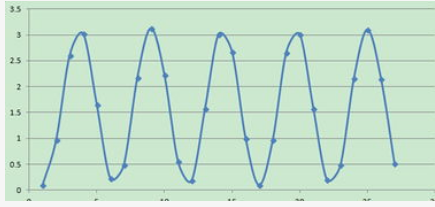

1/14HZ = 71.4ms,一个周期采样6000个点,则每两个点之间的采样间隔为:71.4ms/6000 = 71.4 / 6 us; 选择ADC的采样周期为71.5,则ADC

2019-10-14 16:22

Mixing mode是一些高速DAC中使用的专有采样模式。在传统的DAC中,使用双开关在每个DAC时钟周期对数据进行

2023-08-01 10:53

过采样和数字滤波有助于降低对ADC前置的抗混叠滤波器的要求。重构DAC可以通过类似的方式运用过采样和插值原理。例如,数字音频CD播放器常常采用过采样,其中来自CD的基本

2021-08-25 14:53

前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容: 时钟抖动的构成 时钟

2021-04-07 16:43