ADI最新一代高速DAC具有出色的相位噪声,可在下一代低相位噪声、快速跳频捷变RF/微波频率合成器中实现尺寸、重量、功耗/性能和成本优势。一个挑战是,为了实现这种DAC功能,固定DAC

2022-12-15 15:20

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。

2012-04-01 10:19

接收机ADC对接收到的连续波形进行采样,发射机的DAC与接收机的ADC不可能具有完全相同的时钟频率和相位。时域的采样偏差导致频域上子载波不再正交,对于OFDM来说这是致

2017-02-11 14:16

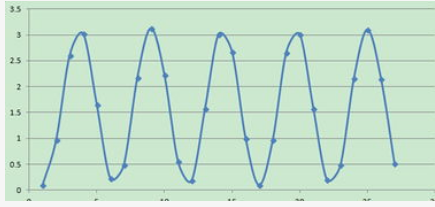

1/14HZ = 71.4ms,一个周期采样6000个点,则每两个点之间的采样间隔为:71.4ms/6000 = 71.4 / 6 us; 选择ADC的采样周期为71.5,则ADC

2019-10-14 16:22

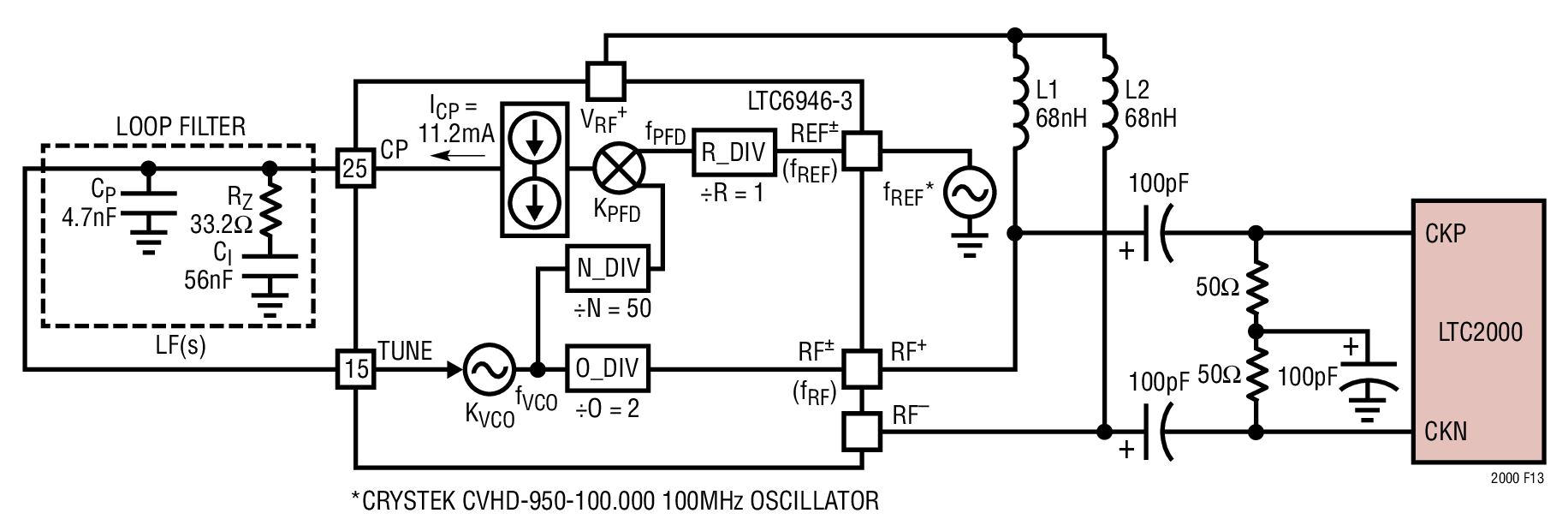

最大化频段中可能的通道数至关重要。高速DAC需要一个干净的采样时钟,以实现最佳的噪声和杂散性能。使用 LTC6946 杂散 PLL 频率合成器作为 LTC2000 的时钟

2023-01-05 15:55

当信号从A输入端口输入时,就意味着使用ADC A和ADC B通道对输入的模拟信号进行采样,双通道组态内部时钟电路(Clock Circuit)为ADC A通道提供内部采样时钟

2023-02-22 11:11

高性能音频数模转换器(DAC)传统上需要一个非常干净的采样主时钟(MCLK),以避免音频质量下降。时钟源通常直接来自晶体振荡器,其产生的抖动通常小于100ps。在某些系

2023-02-28 13:43

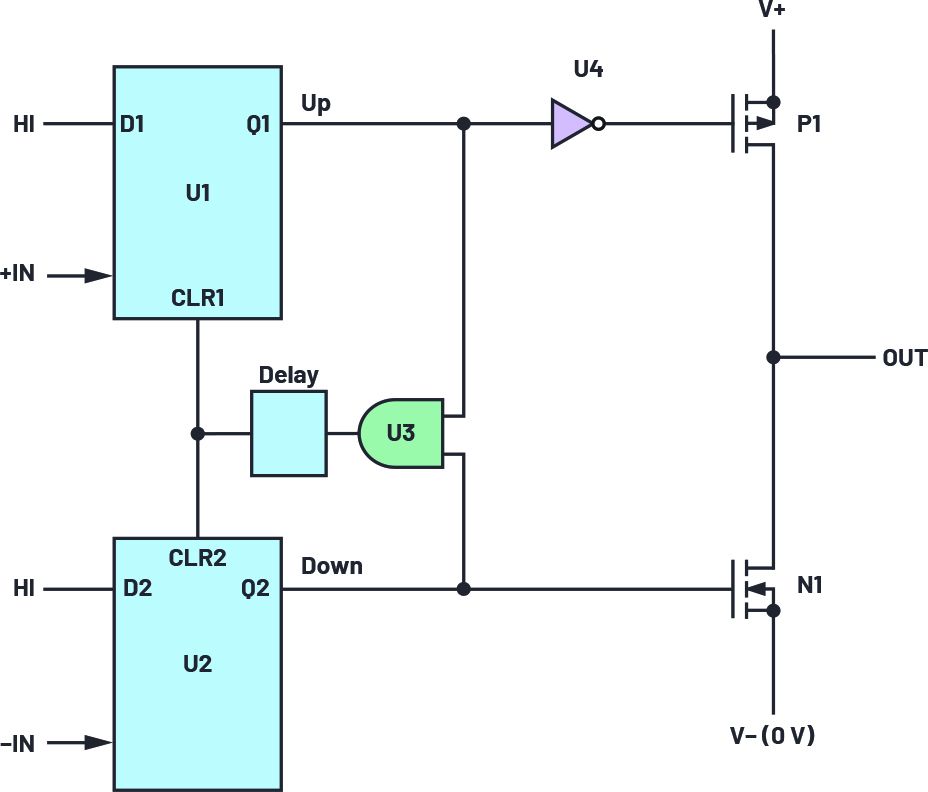

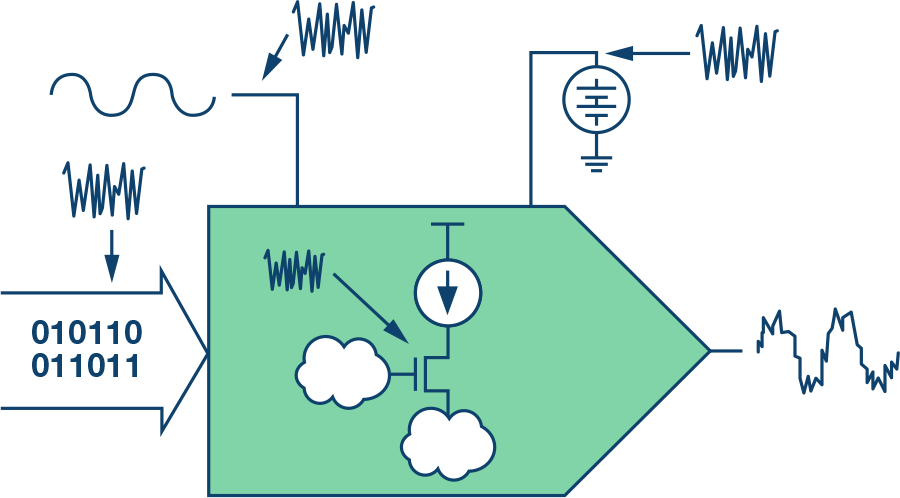

从一张白纸开始,DAC首先被视为一个块盒。噪声可以在内部产生,因为任何实际组件都会产生一些噪声,或者噪声可能来自外部来源。外部电源的入口可以通过任何DAC连接实现,这些连接通常包括电源、时钟和数字接口。这些可能性如图

2023-01-04 15:55

大家好,我是痞子衡,是正经搞技术的痞子。今天痞子衡给大家分享的是i.MXRT中FlexSPI外设不常用的读选通采样时钟源 - loopbackFromSckPad。

2022-11-21 14:15

倍以上,但在电阻抗多频及参数成像技术中正交序列数字解调法的抗噪性能对信号每周期的采样点数决定,采样点数越多,抗噪性能越高。当采样信号频率很高时,为了在被采样信号的一周

2018-11-08 09:56