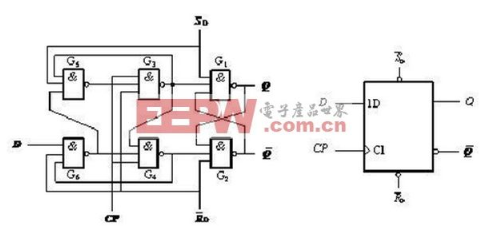

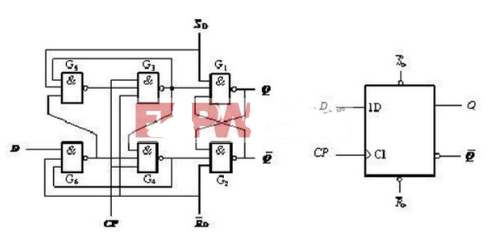

在分析维持-阻塞边沿D触发器的工作原理之前,让我们先来看看 R0的复位功能 、S0的置位功能是如何实现的吧。

2020-10-18 11:26

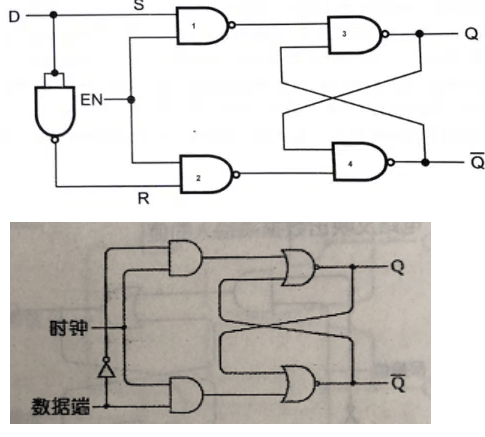

上图是用与非门实现的D触发器的逻辑结构图,CP是时钟信号输入端,S和R分别是置位和清零信号,低有效; D是信号输入端,Q信号输出端;

2022-09-19 15:22

D触发器(D flip-flop)可以存储一位二进制数据的状态,因此具有记忆功能。D触发器通常用于数字电路中,用于实现寄

2023-11-29 14:52

D触发器(D Flip-Flop)是一种数字电子电路,用于延迟其输出信号(Q)的状态变化,直到时钟输入信号的下一个上升沿出现。

2023-12-04 15:23

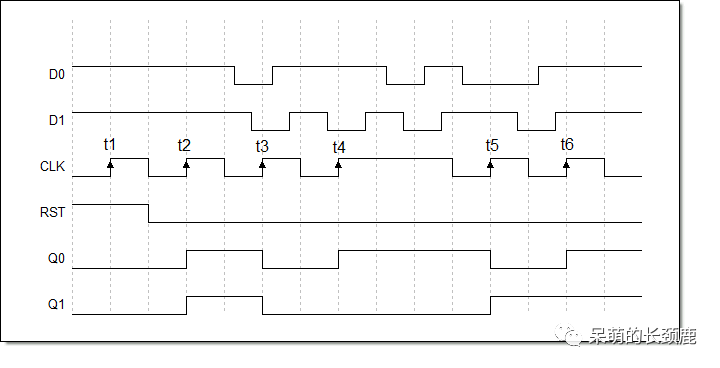

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP

2019-07-12 08:50

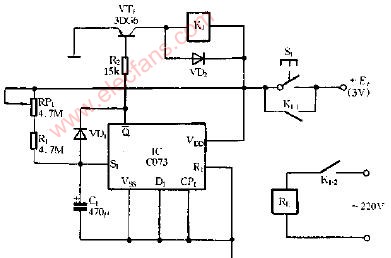

D触发器构成的定时电路图

2009-05-08 15:15

D触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

2023-10-09 17:26

D 触发器或数据触发器是一种触发器,它只有一个数据输入“D”和一个时钟脉冲输入, 这种

2023-01-06 14:19

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D

2023-07-25 10:45

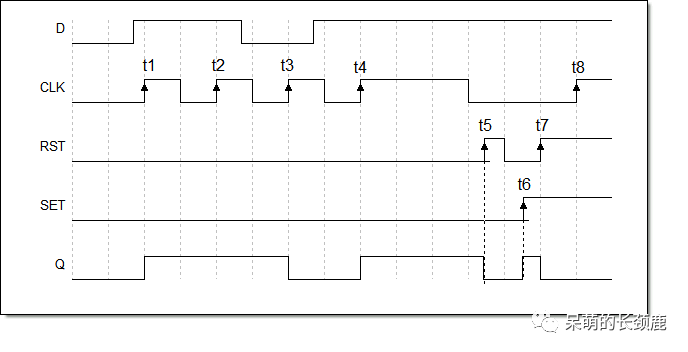

FF_DRE是一个具有异步设置(SET)和重置(RST)输入的边缘触发的D触发器(D Flip-Flop)

2023-12-04 15:47