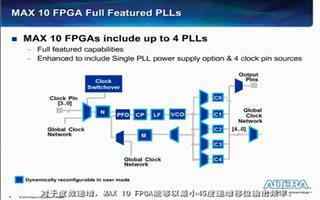

MAX 10 FPGA PLL和时钟培训,此次培训涉及到器件系列的时钟特性和选项。有20个全局时钟网络,全局CLK输入引脚数量也可以加倍,用作通用IO引脚。并且采用动态用户控制进行各种选择和电源控制,构建鲁棒的时钟网络源。它所有4个

2018-06-20 08:00

模拟PLL,模拟PLL是什么意思 所谓模拟PLL,就是说数字PLL中的各个模块的实现都是以模拟器件来实现的,是一个模拟

2010-03-23 10:52

数字PLL,什么是数字PLL 数字PLL PLL的概念 我们所说的PLL,其实就是锁相环路,简称为锁相环。许多

2010-03-23 10:50

普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

2017-02-09 12:54

锁相环(PLL),锁相环(PLL)是什么意思 PLL的概念 我们所说的PLL。其

2010-03-23 10:47

易灵思的FPGA在生成PLL的方式与别的厂家稍有区别,这与其的core和interface架构是相对应的。对于易灵思的FPGA来讲,PLL,GPIO,MIPI,LVDS和DDR相对于core部分都是

2025-06-07 16:18

CPU频率 以Windows系统为例,可以通过电源管理选项来调节CPU的频率。具体步骤如下: 打开控制面板 : 在Windows系统中,点击“开始”菜单,选择“控制面板”。 选择电源

2025-02-01 15:02

PLL是Phase Locked Loop的缩写,中文译作锁相环。它是一种用于控制频率和相位的电路,通过检测和跟踪输入信号的频率和相位,并将其转换为一个稳定的输出信号,从而实现频率和相位的同步与控制。以下是对PLL的详细解析,包括其定义、分类、工作原理、作用以及在

2024-08-16 17:03

pll倍频最大倍数 PLL倍频是一种常见的电路设计技术,通常用于将信号的频率提高到需要的倍数。PLL倍频的实现原理比较复杂,通常需要使用精密的电路元件、时钟信号以及数字信号处理器。本文将详细介绍

2023-09-02 14:59

频率的产生有两种方法:DDS和PLL,但是为什么射频工程师一般用PLL多,很少用DDS呢?

2023-06-28 09:38