变频器频率上不去的原因可能有多种,以下是一些常见的原因。

2023-10-26 09:24

本文给出了DSP多SPI端口通信的设计与实现过程,讨论了其中的关键技术问题。SPI多端口通信方法基于CPLD实现,易移植,易于实现功能扩展,可广泛应用于各种采用SPI通

2011-05-30 11:22

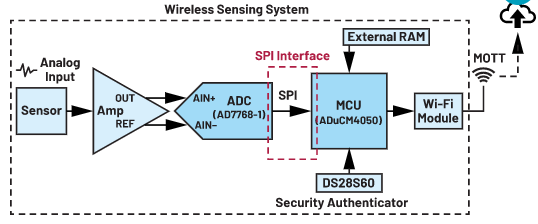

本文利用选定的ADC(AD7768-1)和MCU(ADuCM4050或MAX32660)通过SPI实现了高速的数据事务处理。为实现速率优化的目标,本文简化了ADI的SPI驱动程序执行数据事务处理

2023-06-12 15:26

CPLD内部施密特触发器电器特性见表1。目前大部分使用的CPLD都需要两个电源VCC和VCCIO,VCC就是CPLD内部的核电压,VCCIO是CPLD所有I/O 引脚电

2018-05-11 08:22

STM32 通过 FSMC 读写CPLD 的程序,CPLD挂在STM32的地址线和数据线上,将CPLD看做片外RAM的方式来进行读写,在我做的板子上CPLD挂在第四个区

2018-04-20 10:38

都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果。

2023-05-18 08:56

FPGA LAB和CPLD的LAB设计不同。CPLD LAB由宏单元构成,包括自己的本地可编程阵列,而FPGA LAB由大量的逻辑模块构成,这些模块被称为逻辑单元,即LE,而且本地互连和逻辑分开。LE看起来可能和CPLD

2018-04-17 17:02

AMD公司最先生产带有宏单元的可编程逻辑器件PAL22V10。目前PAL22V10已成为划分PLD的界限。可编程逻辑器件所包含的门数大于PAL22V10所包含则门数,就被认为是复杂可编程逻辑器件,即CPLD。

2018-05-24 01:39

CPLD和FPGA都是由逻辑阵列模块构成的,但是CPLD的LAB基于乘积和宏单元,而FPGA的LAB使用基于LUT的逻辑单元。CPLD的LAB围绕中心全局互连排列,随着器件中逻辑数量的增加,呈指数

2024-01-23 09:17