电子发烧友

5833次浏览

ARM架构通过支持协处理器来扩展处理器的功能。ARM架构的处理器支持最多16个协处理器,通常称为CP0~CP15。下述的协处理器被ARM用于特殊用途。

2023-10-31 16:07

CP15 - STANDARD CAPACITANCE TVS ARRAY - Protek Devices

2022-11-04 17:22

用物理地址),也可以使用其他技术提供功能更为强大的存储系统。##CP15,即通常所说的系统控制协处理器(System Control Coprocesssor)。它负责完成大部分的存储系统管理。##CP15在SWI中进行模式切换的例子。##

2014-08-14 11:40

之前我们在学习MMU的时候, **知道这个内存的分配和CP15协处理器** 。这里先介绍一下CP15寄存器以及访问CP15寄存器的汇编指令。

2023-09-08 17:50

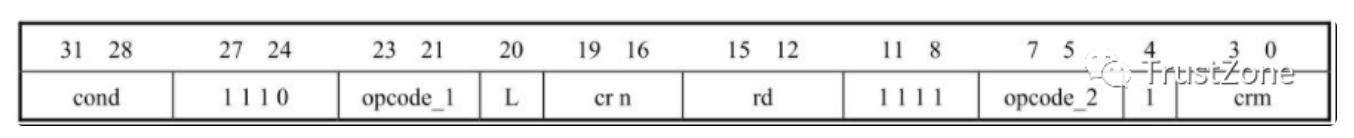

在基于ARM的嵌入式应用系统中,存储系统通常是通过系统控制协处理器CP15完成的。CP15包含16个32位的寄存器,其编号为0~15。访问CP15寄存器的指令MCR A

2022-05-17 14:38

ARM存储系统有非常灵活的体系结构,可以适应不同的嵌入式应用系统的需要。ARM存储器系统可以使用简单的平板式地址映射机制(就像一些简单的单片机一样,地址空间的分配方式是固定的,系统中各部分都使用物理地址),也可以使用其他技术提供功能更为强大的存储系统。比如: 系统可能提供多种类型的存储器件,如FLASH、ROM、SRAM等; Caches技术; 写缓存技术(write buffers); 虚拟内存和I/O地址映射技术。 大多数的系统通过下面的方法之一实现对复

2017-10-17 16:34

ARM的MMU主要实现什么功能?协处理器cp15主要主要实现何功能?简述MMU使能时存储访问过程

2021-03-16 07:57

一、ARM中对于存储管理的协处理器CP15CP15可以包含16个32bit的寄存器,分别标记为0~15。但是对于同一个寄存器的物理寄存器可能会对应多个。实际上对于CP15的访问的指令相当简单,只有

2022-05-17 14:19

1、通过一段MMU的创建来说明MMU的工作方式下面这段代码是OAL进入kernel Start的一段代码,它也就是wince的页表初始化代码,涉及到两部分内如,分别为二级页表的创建和一级页表的创建。这里的一级页表和前面那个有些不同是TTB发生改变了,也就是说系统进入内核后从新创建了页表。;-------------------------------------------------------------------------------; KernelStart - kernel main entry point;; The OEM layer will setup any platform or CPU specific configuration that is; required for the kernel to have access to ROM and DRAM and jump here to start up; the system. Any processor specific cache or MMU initialization should be completed.; The MMU and caches should not enabled.;; This routine will initialize the first-level page table based up the contents of; the MemoryMap array and enable the MMU and caches.;; NOTE: Until the MMU is enabled, kernel symbolic addresses are not valid and must be; translated via the MemoryMap array to find the correct physical address.;; Entry(r0) = pointer to MemoryMap array in physical memory; Exit returns if MemoryMap is invalid;-------------------------------------------------------------------------------LEAF_ENTRY KernelStart原作者:jianwen01

2022-05-18 16:19

1、基于二级页表的地址查询方式 上节讨论了当一级描述符[1:0]为01或者11的时候表示这是一种二级页表查询方式,而一级页表描述符仅仅做为二级页表的索引。下面我们将coarse page与fine page 一起讨论,并且之处他们的区别。 Coarse page 索引了一个二级页表,这个页表描述查询是用大页,小页还是极小页。粗颗粒将1MB的空间划分为256个4KB的空间。如下图所示:其中各个权限的控制位定义如下原作者:jianwen01

2022-05-17 14:29