您好,我正在使用 CYT2B9,请问可以使用 IAR + J-link 进行 Corex-M4 工程的调试吗? 我们目前的情况是只能使用 IAR+J-link调试 Cortex-M0 的工程,调试 Cortex-M4 的工程时会依次弹出两个错误窗口。如下图所示。 错误窗口1错误窗口2

2024-02-02 08:31

年底前,Intel和AMD还将有一次“火星撞地球”的新品较量,均来自各自的发烧级CPU平台。

2019-11-04 11:51

MTK 1.3G Corex-M53

2017-01-23 21:02

COREX WIRE STRIPPER KIT 3CSKWH

2023-03-29 20:14

,寄存器将SRCCx和相应的SRCSx 位同时置0 。创龙提供的例程中,CORE0使用IPCIntGenerate(CPU_CoreX, Core0_Notify_CoreX)函数将IPC 中断生成

2018-12-05 14:06

南加州大学的研究人员利用”相关性解释(Correlation Explanation,CorEx)“的机器学习方法,发现了阿尔茨海默症的“隐藏因素”。这项题为“发现衰老大脑中阿尔茨海默症风险的生物学相关外周特征”的研究发表在杂志《Frontiers in Aging Neuroscience》。

2019-02-15 11:16

浦钢搬迁罗泾工程项目被列为上海市“世博”搬迁工程第二号重点工程,同时也是世界首座年产150万吨铁水的COREX C3000炼铁新技术示范工程,深受业内及公众关注,而在此项目中,西门子分析仪表分别在其煤粉仓CO含量测量,炉气H2分析上有所应用。

2020-08-21 10:41

的地址,即比如corex要访问自己的L2 SRAM,都可以用0x0800000这个地址,但是如果core1, core2 要访问core3的L2 SRAM ,就必须用Memory Map Summary中的CorePac3 L2 SRAM地址,即13800000?

2018-06-21 17:19

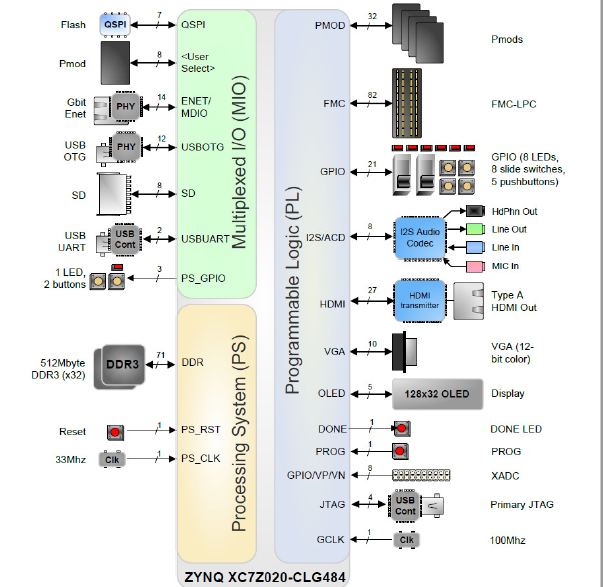

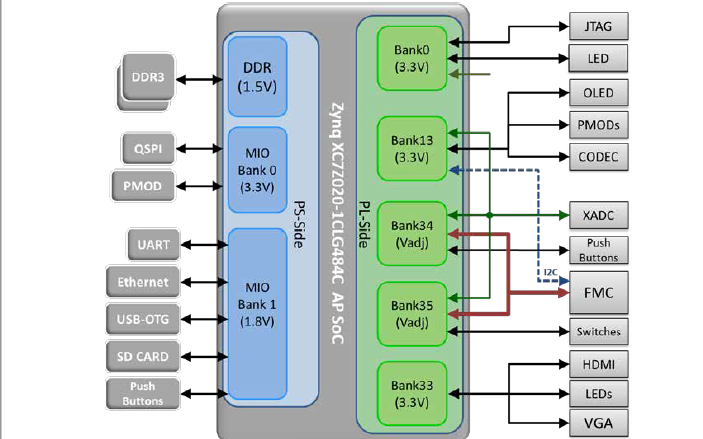

Zedboard是一个基于Xilinx Zynqtm-7000全可编程SoC(AP SoC)的评估和开发板,它结合了一个双COREX-A9处理系统(PS)和85000系列7可编程逻辑(PL)单元

2019-02-13 17:16

Zedboard是一个基于Xilinx Zynqtm-7000全可编程SoC(AP SoC)的评估和开发板,它结合了双COREX-A9处理系统(PS)和85000系列7可编程逻辑(PL)单元,可以在

2019-02-12 17:20