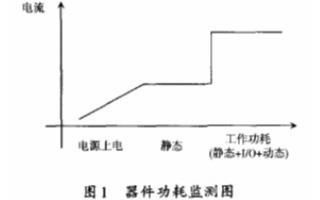

功耗一般由两部分组成:静态功耗和动态功耗。静态功耗也称为待机

2020-01-16 09:46

静态功耗是指一个电路维持在一个或另一个逻辑状态时所需的功率。可以通过观察电路中每个电阻元件的电流I和压降V来计算每个元件的功率VI,并求和得到总功率,这就是没有负载的情况下的静态

2019-07-16 14:41

功耗是我们关注的设计焦点之一,优秀的器件设计往往具备低功耗特点。在前两篇文章中,小编对基于Freez技术的低功耗设计以及FPGA低

2021-02-14 17:50

为设计寻找“完美”FPGA 的重要性日渐升级,其中功耗已成为主要考虑因素。功耗管理在大部分应用中都非常关键。某些标准已为单卡或者单个系统设定了功耗上限。鉴于此,设计人员

2017-11-22 15:03

总的片上功耗 Total On-Chip Power: 总的片上功耗是器件内部的功耗,等同于器件的静态功耗加上设计

2024-03-27 11:32

静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为

2022-09-27 14:45

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和

2017-11-18 03:11

对于研发人员而言,大家总是在追求低功耗设计。采用低功耗设计,无疑是能够带来诸多好处。为帮助大家了解如何降低功耗,本文中,小编将对降低FPGA

2020-12-12 09:08

设计者通过优化自己的设计和注意某些具体情况,可以在FPGA设计中实现低功耗。通过一款具体的FPGA产品了解其低功耗的解决方式,为设计提供了指导。

2017-11-23 10:37

对于FPGA来说,设计人员可以充分利用其可编程能力以及相关的工具来准确估算功耗,然后再通过优化技术来使FPGA和相应的硬件设计满足其功耗方面的要求。

2022-12-29 14:46