本文给出了用可编程逻辑器件GAL配合ISA总线模拟I2C总线时序来对FI1256 MK2进行控制的方法。该方法与PCI总线进行模拟的方法相类似。

2012-03-27 11:33

向量和动态仿真 。本文将介绍静态时序分析的基本概念和方法,包括时序约束,时序路径,

2023-06-28 09:38

静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。

2019-09-01 10:45

静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为

2022-09-27 14:45

静态分析和动态分析是一种双管齐下的方法,可以在可靠性、错误检测、效率和安全性方面改进开发过程。为什么它们都很重要?它们又有什么区别呢?

2023-05-16 16:03

本文介绍了在低功耗系统中降低功耗同时保持测量和监控应用所需的精度的时序因素和解决方案。它解释了当所选ADC是逐次逼近寄存器(SAR)ADC时影响时序的因素。对于Σ-Δ(∑-Δ)架构,时序考虑因素有所不同(请参阅本系列

2022-12-13 11:20

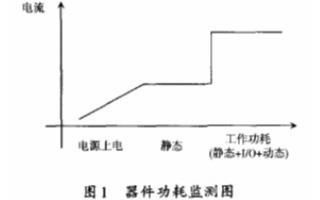

功耗一般由两部分组成:静态功耗和动态功耗。静态功耗也称为待机功耗,是指逻辑门没有开关活动时的功率消耗,主要是由晶体管的漏电流引起,由源极到漏极的漏电流以及栅极到衬底的漏电流组成,图1中

2020-01-16 09:46

动态IP和静态IP的区别在于:动态IP需要在连接网络时自动获取IP地址以供用户正常上网,而静态IP是ISP在装机时分配给用户的IP地址,可以直接连接上网,不需要获取IP

2017-12-27 11:14

大小。它广泛地应用在信号采集和处理、通信、自动检测和多媒体技术等领域。本文介绍AD静态参数和动态参数的测试方法。

2018-01-09 15:05