TTL、CMOS电平和OC门知识大全

2018-07-15 10:33

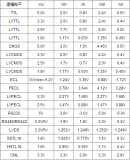

输入高电平门限Vih:保证逻辑门的输入为高电平时所允许的最小输入

2018-03-10 09:47

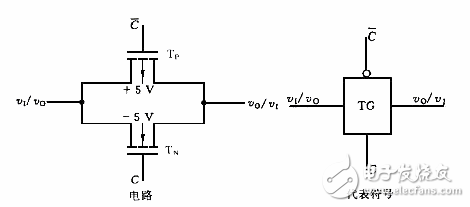

门由一个PMOS和一个NMOS管并联构成,其具有很低的导通电阻(几百欧)和很高的截止电阻(大于10^9欧)。所谓传输门(TG)就是一种传输模拟信号的模拟开关。

2018-04-08 14:06

高阻态这是一个数字电路里常见的术语,指的是电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,

2017-12-25 11:27

COMS集成电路是互补对称金属氧化物半导体(Compiementary symmetry metal oxide semicoductor)集成电路的英文缩写,电路的许多基本逻辑单元都是用增强型PMOS晶体管和增强型NMOS管按照互补对称形式连接的,静态功耗很小。COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许±10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0,扇出数为10--20个COMS门电路。

2017-08-26 10:02

数字信号才是0和1 。凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作 3.3V→5V 电平转换,这是由于 3.3V

2017-08-26 16:52

原理可理解为:单片机一上电的瞬间,电容相当于短路,所以5V电压全部集中在4.7K电阻上,然后,电容开始充电,当充电到一定时候,5V电压基本都集中在电容上了,电阻上的电压低于单片机需要的高电平电压。

2018-07-15 10:36

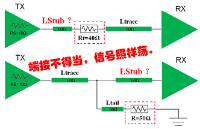

在从事PCB设计之初,我们可能经常会听到这些说法:串联端接电阻需要靠近源端摆放,并联端接电阻需要靠近末端摆放。不明所以的小白就只能直接照做。但在实际项目设计中又可能经常会有困惑,芯片周围已经没有空间了,电阻往外面摆放

2023-02-27 17:29

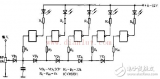

, ZIN是接收器的输入阻抗。 PS:这里仅显示CMOS和PECL/LVPECL电路。 串行端接 实际上,因为阻抗会随频率动态变化,难以达到阻抗匹配,所以缓冲器输出端可以省去电

2019-11-11 15:55

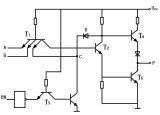

通过双极性晶体管,集电极由上拉电阻接到电源,输入的高电平的电压值就是电源电压值。以MiniARM核心板与GPRS模块为例,如图1所示。

2018-02-14 07:50