半导体)管道组成。在CMOS电路中,输入信号的高和低电平取决于输入信号的电压和电路中的配置。 对于CMOS

2024-02-22 11:12

在 同样5V电源电压情况下,COMS电路可以直接驱动TTL,因为CMOS的输出高电平大于2.0V,输出低

2017-09-20 10:04

TTL器件输出低电平要小于0.8V,高电平要大于2.4V。输入,低于1.2V就认为是0,高于2.0就认为是1。于是TTL

2022-08-22 10:10

和特点 TTL电平是一种数字逻辑电平标准,最初由德州仪器(Texas Instruments)开发。它定义了逻辑“0”(低电平)和逻辑“1”(高电平)的电压范围。在TT

2025-01-16 10:28

数字电路中,把电压的高低用逻辑电平来表示。逻辑电平包括高电平和低电平这两种。不同的元器件形成的数字

2017-11-14 10:37

CMOS逻辑门电路 CMOS逻辑门电路是在TTL电路问世之后 ,所开发出的第二种广泛应用的数字集成器件,从发展趋势

2009-04-06 23:25

请注意LS和CMOS之间的高电平的不兼容性。

2022-03-11 10:28

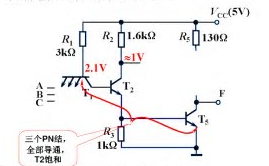

基于双极型晶体管的数字逻辑电路,其工作原理是利用晶体管的开关特性来实现逻辑运算。在TTL门电路中,输入信号通过晶体管的基极-发射极结进行放大,然后通过集电极-发射极结进行开关控制,最终在输出端产生高电平或低

2024-07-30 14:54

TTL电平与CMOS电平的区别 1,TTL电平: 输出高电平>2.4

2007-10-10 12:26

的CMOS电平一般分为逻辑高电平(High Level)和逻辑低电平(Low Level)。CMOS

2024-02-22 11:10