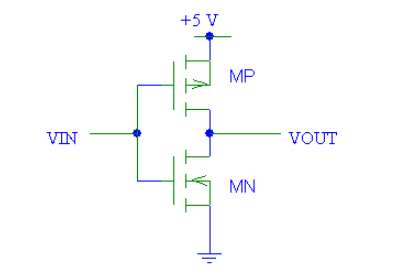

参考上面的CMOS反相器图,由于CMOS器件输入端的电压在5伏和0伏之间变化,因此PMOS和NMOS的状态将相应地不同。

2021-01-21 11:37

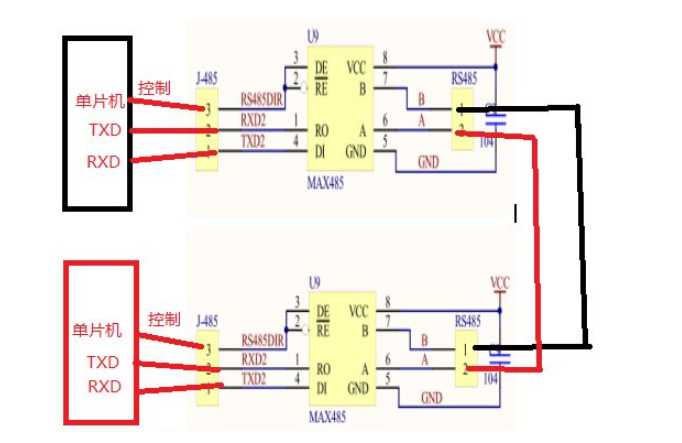

,噪声容限为1.8V,高于3.5V为高电平,噪声容限高为1.8V。比TTL有更高的噪声容限。 2、RS485标准 逻辑1的电平为+2~+6V,逻辑0的电平为-2~-6V, 双向传输,半双工通讯

2017-08-26 17:08

CMOS门电路CMOS门电路一般是由MOS管构成,由于MOS管的栅极和其它各极间有绝缘层相隔,在直流状态下,栅极无电流,所以静态时栅极不取电流,输入电平与外接电阻无关。

2017-11-16 01:49

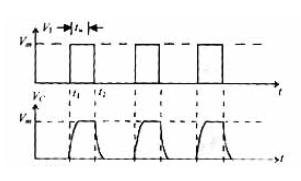

规定的TTL电平高平是2.4V,低电平是0.4V。因为噪声容限的存在,2V也认为是高电平 0.8V也认为是低电平,噪声容限越大说明容许的噪声越大,电路的抗干扰性越好。

2020-03-22 16:43

什么是TTL电平、CMOS电平、RS232电平?它们有什么区别呢?一般说来,CMOS电平比TTL电平有着更高的噪声容限。

2023-02-07 14:58

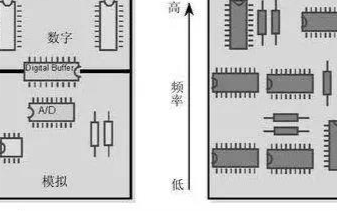

在每个PCB设计中,电路的噪声部分和“安静”部分(非噪声部分)要分隔开。一般来说,数字电路“富含”噪声,而且对

2020-03-06 11:39

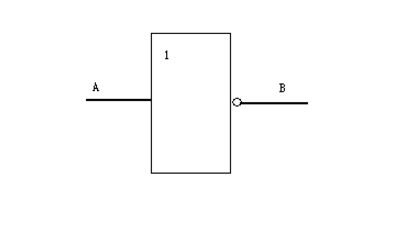

本文开始对门电路的定义和门电路的性质进行了介绍,其次介绍了门电路的结构类型,最后阐述了门电路的作用及分析了门电路有几种

2018-03-01 11:20

提出一种新型的6管SRAM单元结构,该结构采用读/写分开技术,从而很大程度上解决了噪声容限的问题

2011-11-22 14:50

CMOS和非门电路的输入端电阻模式之间存在一些关键的区别,这些区别主要体现在电阻的作用、连接方式以及对电路性能的影响上。

2024-10-01 17:32

1.CMOS电平: ‘1’逻辑电平电压接近于电源电压,‘0’逻辑电平接近于0V。噪声容限很大 2.TTL电平: 输出高电平》2.4V,输出低电平《0.4V。在室温下,一般输出高电平是3.5V

2019-09-14 10:52