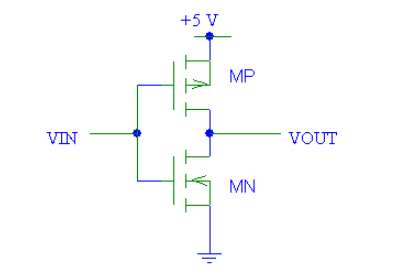

参考上面的CMOS反相器图,由于CMOS器件输入端的电压在5伏和0伏之间变化,因此PMOS和NMOS的状态将相应地不同。

2021-01-21 11:37

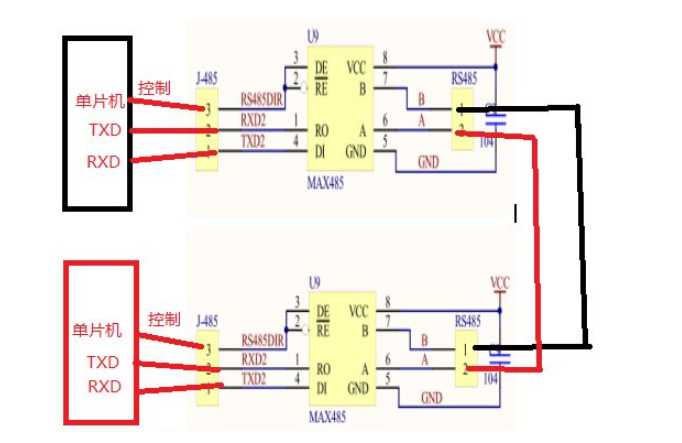

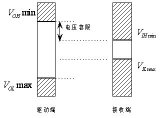

,噪声容限为1.8V,高于3.5V为高电平,噪声容限高为1.8V。比TTL有更高的噪声容限。 2、RS485标准 逻辑1的电平为+2~+6V,逻辑0的电平为-2~-6V, 双向传输,半双工通讯

2017-08-26 17:08

什么是TTL电平、CMOS电平、RS232电平?它们有什么区别呢?一般说来,CMOS电平比TTL电平有着更高的噪声容限。

2023-02-07 14:58

1.CMOS电平: ‘1’逻辑电平电压接近于电源电压,‘0’逻辑电平接近于0V。噪声容限很大 2.TTL电平: 输

2019-09-14 10:52

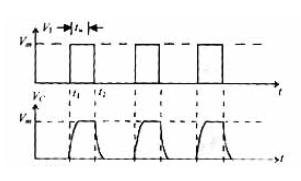

规定的TTL电平高平是2.4V,低电平是0.4V。因为噪声容限的存在,2V也认为是高电平 0.8V也认为是低电平,噪声容限越大说明容许的噪声越大,电路的抗干扰性越好。

2020-03-22 16:43

在高速pcb设计中,有很大一部分工作是进行噪声预算,规划系统各种噪声源产生噪声大小。这就涉及到一个非常基础但十分重要的概念:电压

2018-07-19 17:32

提出一种新型的6管SRAM单元结构,该结构采用读/写分开技术,从而很大程度上解决了噪声容限的问题

2011-11-22 14:50

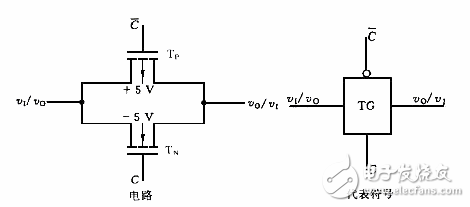

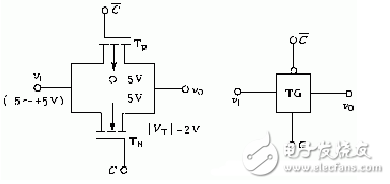

本文主要介绍了cmos传输门如何传输(cmos传输门工作原理及作用_真值表),CMOS传输

2018-04-08 14:06

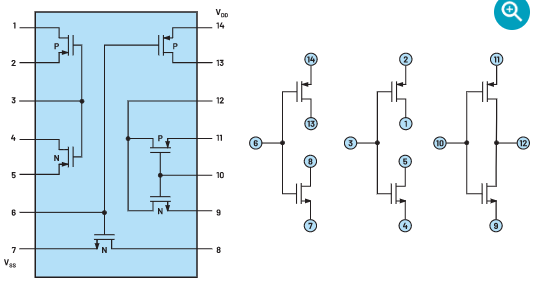

本文主要介绍了cmos传输门芯片型号有哪些?重点介绍了四联双向开关CC4016cmos传输门芯片。CMOS传输

2018-04-08 14:27

本实验活动的目标是进一步强化上一个实验活动 “使用CD4007阵列构建CMOS逻辑功能” 中探讨的CMOS逻辑基本原理,并获取更多使用复杂CMOS门级电路的经验。具体而

2023-05-29 14:17