PMOS晶体管和增强型NMOS管按照互补对称形式连接的,静态功耗很小。COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许±10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0,扇出数

2017-08-26 10:02

数字信号才是0和1 。凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作 3.3V→5V 电平转换,这是由于 3.3V CMOS 的

2017-08-26 16:52

1.CMOS电平: ‘1’逻辑电平电压接近于电源电压,‘0’逻辑电平接近于0V。噪声容限很大 2.TTL电平:

2019-09-14 10:52

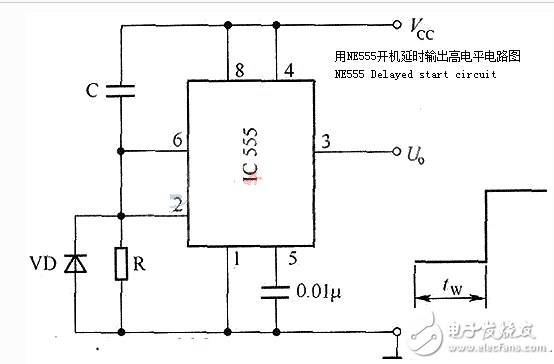

本文主要介绍了ne555延时电路图大全(开机延时输出高电平/自激多谐振荡器)。IC1555时基电路接成占空比可调的自激多谐振荡器。当按下按钮SB后,12V的直流电压加到电路中,由于电容器C6的电压

2018-03-28 16:11

原理可理解为:单片机一上电的瞬间,电容相当于短路,所以5V电压全部集中在4.7K电阻上,然后,电容开始充电,当充电到一定时候,5V电压基本都集中在电容上了,电阻上的电压低于单片机需要的高电平电压。

2018-07-15 10:36

TTL、CMOS电平和OC门知识大全

2018-07-15 10:33

逻辑电平输出是数字电路中的一个重要概念,它涉及到数字信号的表示和传输。在数字电路中,逻辑电平通常指的是电路中用于表示二进制数字(0和1)的电压水平。逻辑电平

2024-09-20 17:32

1、CMOS电平标准 输出 L: 《0.1*Vcc ; H:》0.9*Vcc。 输入 L: 《0.3*Vcc ; H:》0.7*Vcc. 由于CMOS电源采用12

2017-08-26 17:08

CMOS电平是数字信号,COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许±10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于

2017-08-26 17:26

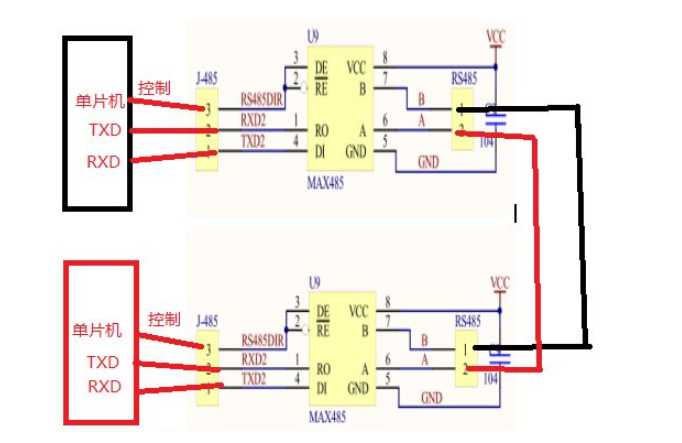

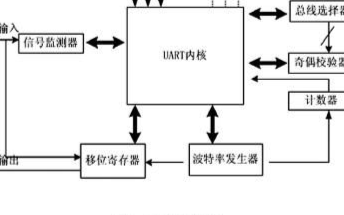

实现RS-232电平和TTL/CMOS电平转换可以用接口芯片来实现,实现数据的串行到并行转换用的是UART,它们是实现串行通信必不可少的两个部分。

2021-03-26 14:19