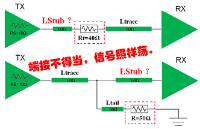

在从事PCB设计之初,我们可能经常会听到这些说法:串联端接电阻需要靠近源端摆放,并联端接电阻需要靠近末端摆放。不明所以的小白就只能直接照做。但在实际项目设计中又可能经常会有困惑,芯片周围已经没有空间了,电阻往外面摆放

2023-02-27 17:29

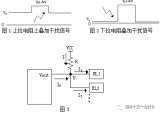

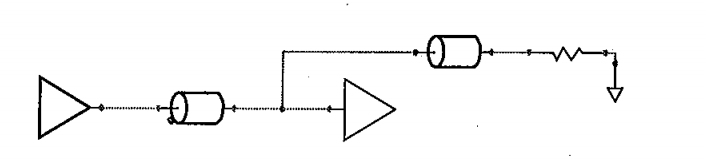

, ZIN是接收器的输入阻抗。 PS:这里仅显示CMOS和PECL/LVPECL电路。 串行端接 实际上,因为阻抗会随频率动态变化,难以达到阻抗匹配,所以缓冲器输出端可以省去电

2019-11-11 15:55

对于驱动TTL集成电路,上拉电阻的阻值要用1~10K之间的,有时候电阻太大的话是拉不起来的,因此用的阻值较小。但是对于CMOS集成电路,上拉

2018-05-26 09:16

CMOS和非门电路的输入端电阻模式之间存在一些关键的区别,这些区别主要体现在电阻的作用、连接方式以及对电路性能的影响上。

2024-10-01 17:32

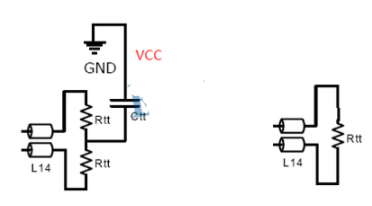

I2C一般为开漏结构,需要在外部加上拉电阻,常见的阻值有1k、1.5k、2.2k、4.7k、5.1

2022-09-02 09:49

末端并联端接的电阻最好放在接收器之后,走线先连接到接收器,然后拉出一条“尾巴”,端接电阻放在“尾巴”后面,如图所示。

2023-03-22 16:16

末端并联端接也用的比较多,如前文提到的T点及Fly_by拓扑,其中上拉比较常见,端接电阻通常和传输线阻抗一致。

2021-04-11 09:56

“上下拉电阻应用很简单吗?”那可不一定。电路设计中,在哪些地方要加上下拉电阻?上下拉电阻加多大呢?是否要考虑它的功耗,以及它的灌电流大小,太大会损坏电子器件。一般情况下,元器件需要上下拉的地方,加4.7

2023-03-17 16:32

本文提供了一种较为常规的使用NTC热敏电阻采集温度的方法。 首先,采用额定温度Tn=25℃时,电阻值为Rn=10K,且热敏指数B=3950的NTC热敏电阻。

2018-05-26 07:53